### **INTERNATIONAL STANDARD**

**ISO** 21111-5

> First edition 2020-06

### Road vehicles — In-vehicle Ethernet —

Part 5:

Optical 1-Gbit/s physical layer system requirements and test plans

Véhicules routiers — Ethernet embarqué —

ances et cique view the click to view the standard service of the control of the Partie 5: Exigences et plans de test du système de couche physique à

#### COPYRIGHT PROTECTED DOCUMENT

© ISO 2020

All rights reserved. Unless otherwise specified, or required in the context of its implementation, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office CP 401 • Ch. de Blandonnet 8 CH-1214 Vernier, Geneva Phone: +41 22 749 01 11 Email: copyright@iso.org Website: www.iso.org

Published in Switzerland

| Co   | ntent                |                                                                                                                                                                                                                                 | Page     |

|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fore | eword                |                                                                                                                                                                                                                                 | <b>v</b> |

| Intr | oductio              | on                                                                                                                                                                                                                              | vi       |

| 1    | Scop                 | oe                                                                                                                                                                                                                              | 1        |

| 2    | •                    | native references                                                                                                                                                                                                               |          |

|      |                      | ns and definitions                                                                                                                                                                                                              |          |

| 3    |                      |                                                                                                                                                                                                                                 |          |

| 4    | -                    | bols and abbreviated terms                                                                                                                                                                                                      |          |

|      | 4.1<br>4.2           | Symbols Abbreviated terms                                                                                                                                                                                                       |          |

| _    |                      | sical layer system requirements and interoperability test setups requirements                                                                                                                                                   |          |

| 5    | <b>Phys</b> 5.1      | Conoral Conoral                                                                                                                                                                                                                 | <b>4</b> |

|      | 5.2                  | GEPOF link status requirements                                                                                                                                                                                                  | 5        |

|      | 0.2                  | 5.2.1 IOP GEPOF REO LINK STATUS 1                                                                                                                                                                                               | 5        |

|      |                      | 5.2.2 IOP_GEPOF_REQ_LINK_STATUS_2                                                                                                                                                                                               | 5        |

|      | 5.3                  | GEPOF link-up requirements                                                                                                                                                                                                      | 5        |

|      |                      | 5.3.1 IOP_GEPOF_REQ_LINK_UP_1                                                                                                                                                                                                   | 5        |

|      |                      | General GEPOF link status requirements 5.2.1 IOP_GEPOF_REQ_LINK_STATUS_1 5.2.2 IOP_GEPOF_REQ_LINK_STATUS_2 GEPOF link-up requirements 5.3.1 IOP_GEPOF_REQ_LINK_UP_1 5.3.2 IOP_GEPOF_REQ_LINK_UP_2 5.3.3 IOP_GEPOF_REQ_LINK_UP_3 | 5        |

|      |                      | 5.3.3 IOP_GEPOF_KEQ_LINK_UP_3                                                                                                                                                                                                   | 5        |

|      |                      | 5.3.5 IOP GEPOF REO LINK UP 5                                                                                                                                                                                                   | 6        |

|      | 5.4                  | Channel quality requirements                                                                                                                                                                                                    | 6        |

|      |                      | 5.3.2 IOP_GEPOF_REQ_LINK_UP_2  5.3.3 IOP_GEPOF_REQ_LINK_UP_3  5.3.4 IOP_GEPOF_REQ_LINK_UP_4  5.3.5 IOP_GEPOF_REQ_LINK_UP_5  Channel quality requirements  5.4.1 IOP_GEPOF_REQ_CH_QLTY_1                                         | 6        |

|      |                      | 5.4.2 IOP_GEPOF_KEQ_CH_QLI I 🚜                                                                                                                                                                                                  | O        |

|      | 5.5                  | Communication reliability under climatic loads requirements                                                                                                                                                                     |          |

|      |                      | 5.5.1 IOP_GEPOF_REQ_RELIABILITY_TEMP_1<br>5.5.2 IOP_GEPOF_REQ_REQABILITY_TEMP_2                                                                                                                                                 |          |

|      |                      | 5.5.3 IOP_GEPOF_REQ_RELIABILITY_TEMP_3                                                                                                                                                                                          |          |

|      |                      | 5.5.4 IOP_GEPOF_REQ_RELIABILITY_TEMP_4                                                                                                                                                                                          |          |

|      |                      | 5.5.5 IOP_GEPOF_REQ_RELIABILITY_TEMP_5                                                                                                                                                                                          | 7        |

|      |                      | 5.5.6 IOP_GEPOF_REQ_RELIABILITY_TEMP_6                                                                                                                                                                                          |          |

|      |                      | 5.5.7 IOP_GEPOF_REQ_RELIABILITY_TEMP_7                                                                                                                                                                                          |          |

|      |                      | 5.5.8 IOP_GEPOF_REQ_RELIABILITY_TEMP_8<br>5.5.9 IOP_GEPOF_REQ_RELIABILITY_TEMP_9                                                                                                                                                |          |

|      |                      | 5.5.10 10P_GEPOF_REQ_RELIABILITY_TEMP_10                                                                                                                                                                                        |          |

|      | 5.6                  | Test set-up requirements                                                                                                                                                                                                        | 9        |

|      |                      | 5.6.1 General                                                                                                                                                                                                                   |          |

|      |                      | \$.6.2 Channel requirements                                                                                                                                                                                                     |          |

|      | ~                    | 5.6.3 Device and LP requirements for interoperability test plan                                                                                                                                                                 | 11       |

| 6    | Inte                 | roperability test plan set-ups                                                                                                                                                                                                  | 13       |

|      | 6.1                  | General                                                                                                                                                                                                                         |          |

|      | 6.2                  | Interoperability test set-up 1                                                                                                                                                                                                  |          |

|      | 6.3<br>6.4           | Interoperability test set-up 2Interoperability test set-up 3                                                                                                                                                                    |          |

|      | 6.5                  | Interoperability test set-up 5                                                                                                                                                                                                  |          |

| 7    |                      |                                                                                                                                                                                                                                 |          |

| 7    | <b>Inte</b> i<br>7.1 | roperability test plan<br>General                                                                                                                                                                                               |          |

|      | 7.1                  | High attenuation channel with climatic load                                                                                                                                                                                     |          |

|      | 7.3                  | Low attenuation channel with climatic load                                                                                                                                                                                      |          |

|      | 7.4                  | Link status time                                                                                                                                                                                                                | 25       |

|      | 7.5                  | Channel quality                                                                                                                                                                                                                 | 28       |

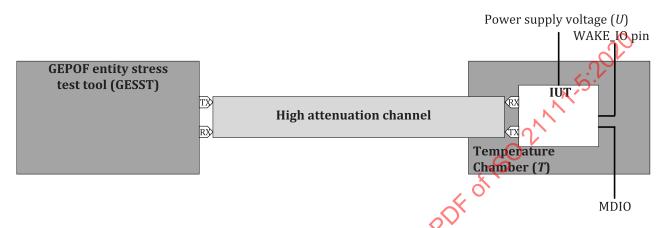

| 8    | Devi                 | ce-level physical layer conformance test set-ups requirements                                                                                                                                                                   | 30       |

|      | 8.1                  | General                                                                                                                                                                                                                         |          |

#### ISO 21111-5:2020(E)

|    | 8.2                                            | Test set-up requirements  8.2.1 IUT requirements for device-level physical layer conformance test plan  8.2.2 GEPOF entity stress test tool requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                   |

|----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 9  | 9.1<br>9.2<br>9.3<br>9.4                       | General  Device-level physical layer conformance test plan set-ups  Device-level physical layer conformance test set-up 1  Device-level physical layer conformance test set-up 2  Device-level physical layer conformance test set-up 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33<br>33<br>34       |

| 10 | Device<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5 | e-level physical layer conformance test plan  General  High attenuation channel  Low attenuation channel  Optical IUT transmitter measurements  Wake-up and synchronized link sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36<br>37<br>43<br>49 |

|    |                                                | 10.5.1 General test cases.  10.5.2 Device with multiple physical entities test cases.  7. Citck to view the full part of the control of the c |                      |

#### Foreword

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular, the different approval criteria needed for the different types of ISO documents should be noted. This document was drafted in accordance with the editorial rules of the ISO/IEC Directives, Part 2 (see <a href="www.iso.org/directives">www.iso.org/directives</a>).

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see <a href="https://www.iso.org/patents">www.iso.org/patents</a>).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation of the voluntary nature of standards, the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT) see <a href="https://www.iso.org/iso/foreword.html">www.iso.org/iso/foreword.html</a>.

This document was prepared by Technical Committee ISO/TC 22, *Road vehicles*, Subcommittee SC 31, *Data communication*.

A list of all parts in the ISO 21111 series can be found on the ISO website.

Any feedback or questions on this document should be directed to the user's national standards body. A complete listing of these bodies can be found at <a href="https://www.iso.org/members.html">www.iso.org/members.html</a>.

#### Introduction

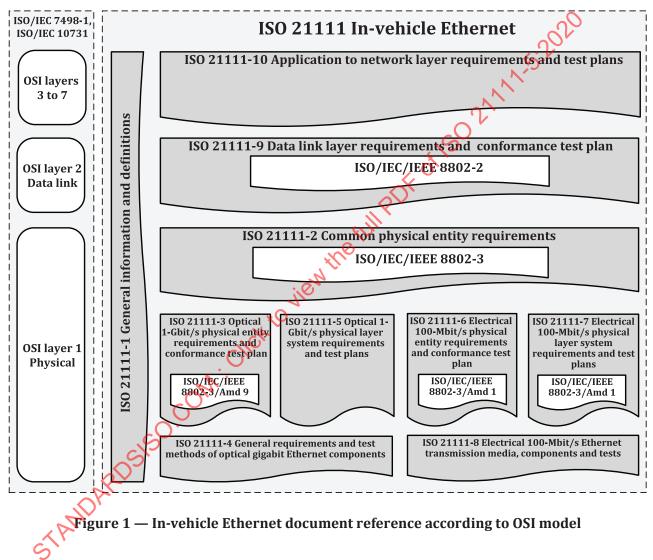

The ISO 21111 series includes in-vehicle Ethernet requirements and test plans that are disseminated in other International Standards and complements them with additional test methods and requirements. The resulting requirement and test plans are structured in different documents following the Open Systems Interconnection (OSI) reference model and grouping the documents that depend on the physical media and bit rate used.

In general, the Ethernet requirements are specified in ISO/IEC/IEEE 8802-3. The ISO 21111 series provides supplemental specifications (e.g. wake-up, I/O functionality), which are required for in-vehicle Ethernet applications. In road vehicles, Ethernet networks are used for different purposes requiring different bit-rates. Currently, the ISO 21111 series specifies the 1-Gbit/s optical and 100-Mbit/s electrical physical layer.

The ISO 21111 series contains requirement specifications and test methods related to the in-vehicle Ethernet. This includes requirement specifications for physical layer entity (e.g. connectors, physical layer implementations) providers, device (e.g. electronic control units, gateway units) suppliers, and system (e.g. network systems) designers. Additionally, there are test methods specified for conformance testing and for interoperability testing.

Safety (electrical safety, protection, fire, etc.) and electromagnetic compatibility (EMC) requirements are out of the scope of the ISO 21111 series.

The structure of the specifications given in the ISO 21111 series complies with the Open Systems Interconnection (OSI) reference model specified in ISO/IEC 7498  $1^{11}$  and ISO/IEC 10731 $1^{12}$ .

ISO 21111-1 defines the terms which are used in this series of standards and provides an overview of the standards for in-vehicle Ethernet including the complementary relations to ISO/IEC/IEEE 8802-3, the document structure, type of physical entities, in-vehicle Ethernet specific functionalities and so on.

ISO 21111-2 specifies the interface between reconciliation sublayer and physical entity including reduced gigabit media independent interface (RGMII), and the common physical entity wake-up and synchronized link sleep functionalities, independent from physical media and bit rate.

ISO 21111-3 specifies supplemental requirements to a physical layer capable of transmitting 1-Gbit/s over plastic optical fibre compliant with ISO/IEC/IEEE 8802-3, with specific application to communications inside road vehicles, and a test plan for physical entity conformance testing.

ISO 21111-4 specifies the optical components requirements and test methods for 1-Gbit/s optical invehicle Ethernet.

This document specifies, for 1-Gbit/s optical in-vehicle Ethernet, requirements on the physical layer at system level, requirements on the interoperability test set-ups, the interoperability test plan that checks the requirements for the physical layer at system level, requirements on the device-level physical layer conformance test set-ups, and device-level physical layer conformance test plan that checks a set of requirements for the OSI physical layer that are relevant for device vendors.

ISO 21111-6 specifies advanced features of an ISO/IEC/IEEE 8802-3 in-vehicle Ethernet physical layer (often also called transceiver), e.g. for diagnostic purposes for in-vehicle Ethernet physical layers. It specifies advanced physical layer features, wake-up and sleep features, physical layer test suite, physical layer control requirements and conformance test plan, physical sublayers test suite and physical sublayers requirements and conformance test plan.

ISO 21111-7 specifies the implementation for ISO/IEC/IEEE 8802-3:2017/Amd 1:2017, which defines the interface implementation for automotive applications together with requirements on components used to realize this Bus Interface Network (BIN). ISO 21111-7 also defines further testing and system requirements for systems implemented according to the system specification. In addition, ISO 21111-7 defines the channels for tests of transceivers with a test wiring harness that simulates various electrical communication channels.

ISO 21111-8 specifies the transmission media, the channel performance and the tests for ISO/IEC/IEEE 8802-3 in-vehicle Ethernet.

ISO 21111-9 specifies the data link layer requirements and conformance test plan. It specifies the requirements and test plan for devices and systems with bridge functionality.

ISO 21111-10 specifies the application to network layer requirements and test plan. It specifies the requirements and test plan for devices and systems that include functionality related with OSI layers from 3 to 7.

Figure 1 shows the parts of the ISO 21111 series and the document structure.

STANDARDS SO. COM. Click to View the full PDF of 150 21111 15:2020

### Road vehicles — In-vehicle Ethernet —

### Part 5:

# Optical 1-Gbit/s physical layer system requirements and test plans

### 1 Scope

This document specifies:

- requirements on the physical layer at system level,

- requirements on the interoperability test set-ups,

- interoperability test plan that checks the requirements for the physical layer at system level,

- requirements on the device-level physical layer conformance test set-ups, and

- device-level physical layer conformance test plan that checks a set of requirements for the OSI physical layer that are relevant for device vendors.

The interoperability test plan checks the physical layer system requirements specified in this document and in ISO/IEC/IEEE 8802-3:2017/Amd 9.

This test plan is structured in four different test groups, attending to the kind of system requirements that covers:

- link status, that includes the tests that check the status of the link by using the content of the available registers and its accuracy with the real status of the link,

- link-up, that includes the tests that check the time that the IUT reaches a reliable link status from certain state,

- channel quality, that includes the tests that check the quality of the optical channel by using the

content of the available registers and its accuracy with the real quality of the optical channel, and

- wake-up and sleep, that include tests that check that the transmission and reception of the wake-up and sleep events.

The device-level conformance test plan checks the device-level requirements specified in the ISO 21111 series and in ISO/IEC/IEEE 8802-3:2017/Amd 9.

This test plan is structured in four different test groups, attending to the test set-up required:

- high-attenuation channel,

- low-attenuation channel,

- optical IUT transmitter measurements, and

- wake-up and synchronised link sleep.

#### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

ISO 21111-1<sup>1)</sup>, Road vehicles — In-vehicle Ethernet — Part 1: General information and definitions

ISO 21111-2<sup>2</sup>], Road vehicles —In-vehicle Ethernet — Part 2: Common medium-independent interface specifications

ISO 21111-3, Road vehicles — In-vehicle Ethernet — Part 3: Optical 1-Gbit/s physical layer specification and conformance test plan

ISO 21111-4, Road vehicles — In-vehicle Ethernet — Part 4: Optical 1-Gbit/s component requirements and test methods

ISO/IEC/IEEE 8802-3, Standard for Ethernet

ISO/IEC/IEEE 8802-3:2017/Amd 9:2018, Physical Layer Specifications and Management Parameters for 1000 Mb/s Operation over Plastic Optical Fiber

#### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in ISO/IEC/IEEE 8802-3, ISO 21111-1 and the following apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- ISO Online browsing platform: available at <a href="https://www.iso.org/obp">https://www.iso.org/obp</a>

- IEC Electropedia: available at <a href="http://www.electropedia.org/">http://www.electropedia.org/</a>

#### 3.1

#### network system

two or more devices connected bi-directionally through a physical medium

Note 1 to entry: Physical medium is defined in ISO 7498-1:1994.

#### 3.2

#### **GEPOF link status**

reliability or unreliability of the bidirectional communication between two GEPOF physical entities as signalled by bit 2 of MDIO register 1.1 specified in ISO/IEC/IEEE 8802-3:2017/Amd 9

#### 3.3

#### device-level physical layer conformance test plan

set of conformance test cases that covers physical layer requirements relevant for the device provider

#### 3.4

#### cable plug

POF cable plug that fulfils the specification in ISO 21111-4

#### 3.5

#### cable socket

POF cable socket that fulfils the specification in ISO 21111-4

<sup>1)</sup> Under preparation. Stage at the time of publication: ISO/DIS 21111-1:2020.

<sup>2)</sup> Under preparation. Stage at the time of publication: ISO/DIS 21111-2:2020.

#### 3.6

#### in-line connector

connector resulting of the match of a cable plug (3.4) and a cable socket (3.5)

#### 4 Symbols and abbreviated terms

#### 4.1 Symbols

For the purposes of this document, the symbols of ISO 21111-1 and the following apply.

*IDD*<sub>device</sub> device current consumption

*IDD*<sub>min</sub> minimum device current consumption in operation

*IDD*<sub>max</sub> maximum device current consumption in operation

*IDD\_DIS*<sub>min</sub> minimum device current consumption in sleep power state(

IDD\_DIS<sub>max</sub> maximum device current consumption in sleep power state

T climatic chamber temperature

$T_{

m device}$  device climatic chamber temperature

$T_{\mathrm{LP}}$  link partner climatic chamber temperature

$T_{\min}$  minimum operating temperature

$T_{\text{max}}$  maximum operating temperature

$T_{\rm typ}$  typical operating temperature

U supply voltage

$U_{

m device}$  device supply voltage

$U_{\rm LP}$  link partner supply voltage

$U_{\min}$  minimum supply voltage

$U_{\rm max}$  maximum supply voltage

$U_{\rm typ}$  typical supply voltage

#### 4.2 Abbreviated terms

For the purposes of this document, the abbreviated terms of ISO 21111-1 and the following apply.

AOP average optical power

ER extinction ratio

GESST GEPOF entity stress test tool

IUT implementation under test

LP link partner

LT lower tester

#### ISO 21111-5:2020(E)

| POF | plastic optical fibre    |  |

|-----|--------------------------|--|

| RIN | relative intensity noise |  |

| RMS | root mean square         |  |

| TC  | test coordinator         |  |

| UT  | upper tester             |  |

# 5 Physical layer system requirements and interoperability test setups requirements

#### 5.1 General

<u>Clause 5</u> specifies the physical layer system requirements and the interoperability test setup requirements.

The physical layer system requirements are structured by the functionality that they cover:

- The GEPOF link status comprises the physical layer system requirements related with the time and accuracy the network system signals a new status in the GEPOF link (see <u>5.2</u>),

- The GEPOF link-up time comprises the physical layer system requirements related with the time the network system signals a reliable GEPOF link status from a given initial power state of the two physical entities involved in the GEPOF link (see 5.3),

- The channel quality comprises the physical layer system requirements related with the time and accuracy the network system signals a change of the channel quality in the GEPOF link (see <u>5.4</u>),

- The communication reliability comprises the physical layer system requirements related with the communication reliability when the devices in the network system are under certain climatic loads and the communication channel is set (see 5.5).

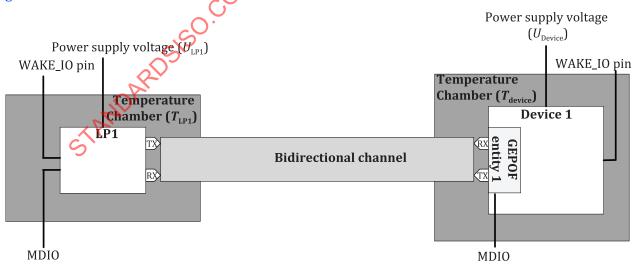

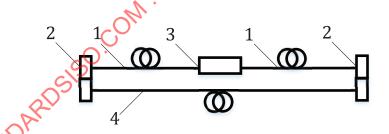

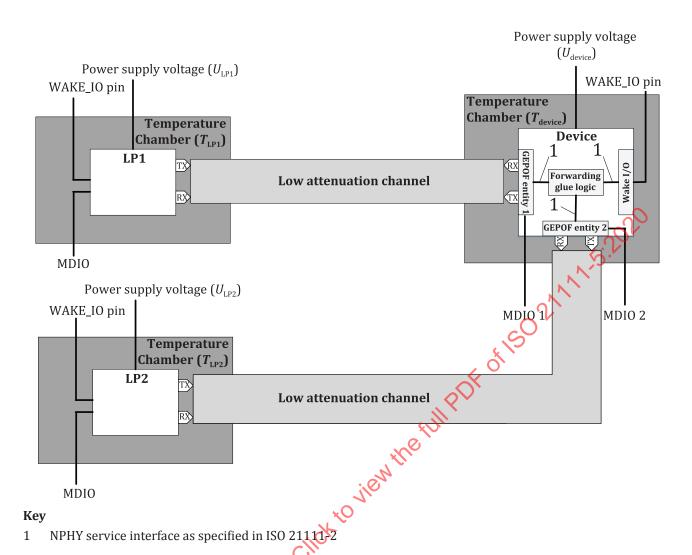

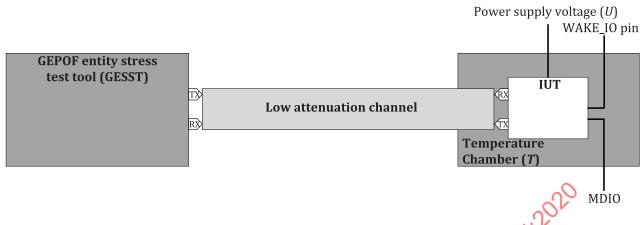

The reference network system used to specify the physical layer system requirements is shown in Figure 2.

Figure 2 — Reference network system for physical layer system requirements definition

The interoperability test set-ups requirements are specified in <u>5.6</u>. They include requirements on the channels that are used in the test set-ups and requirements on the device and LP used in the test set-ups.

#### 5.2 GEPOF link status requirements

#### 5.2.1 IOP\_GEPOF\_REQ\_LINK\_STATUS\_1

#### REQ 1.1 PHY — IOP\_GEPOF\_REQ\_LINK\_STATUS\_1

The time measured from the instant when the GEPOF link status changes to "bidirectional reliable link is established" till the reception of the first Ethernet frame in the device shall be lower than 0,5 ms when Ethernet frames are sent continuously from the LP.

#### 5.2.2 IOP\_GEPOF\_REQ\_LINK\_STATUS\_2

#### REQ 1.2 PHY — IOP\_GEPOF\_REQ\_LINK\_STATUS\_2

The time measured from the instant when the GEPOF link becomes unreliable till the GEPOF link status changes to "bidirectional unreliable link" shall be lower than 5 ms.

#### 5.3 GEPOF link-up requirements

#### 5.3.1 IOP\_GEPOF\_REQ\_LINK\_UP\_1

#### REQ 1.3 PHY — IOP\_GEPOF\_REQ\_LINK\_UP\_1

The time measured from the instant when the GEPOF entity 1 receives a PHY\_WakeUp.request from the data link layer as specified in ISO 21111-2 till the GEPOF link status in GEPOF entity changes to "bidirectional reliable link is established" shall be lower than 100 ms.

The initial power state of the GEPOF entity in device 1 and its LP to measure this time shall be Sleep as defined in ISO 21111-2.

#### 5.3.2 IOP\_GEPOF\_REQ\_LINK\_UP\_2

#### REQ 1.4 PHY — IOP\_GEPOF\_REQ\_LINK\_UP\_2

The time measured from the instant when the GEPOF entity 1 receives a WakeUp\_request event as specified in ISO 21111-2 till the GEPOF link status in GEPOF entity 1 changes to "bidirectional reliable link is established" shall be lower than 100 ms.

The initial power state of the GEPOF entity 1 to measure this time shall be Sleep as defined in ISO 21111-2.

The initial power state of the LP to measure this time shall be Normal as defined in ISO 21111-2.

#### 5.3.3 IOP GEPOF\_REQ\_LINK\_UP\_3

#### REQ\_1.5 PHY — IOP\_GEPOF\_REQ\_LINK\_UP\_3

The time measured from the instant when the GEPOF entity 1 is reset till the GEPOF link status in GEPOF entity 1 changes to "bidirectional reliable link is established" shall be lower than 100 ms.

The initial power state of the GEPOF entity 1 to measure this time shall be Normal as defined in ISO 21111-2.

The initial power state of the LP to measure this time shall be Normal as defined in ISO 21111-2.

#### 5.3.4 IOP\_GEPOF\_REQ\_LINK\_UP\_4

#### REQ 1.6 PHY — IOP\_GEPOF\_REQ\_LINK\_UP\_4

The time measured from the instant when the LP is reset till the GEPOF link status in GEPOF entity 1 changes to "bidirectional reliable link is established" shall be lower than 100 ms.

The initial power state of the GEPOF entity 1 to measure this time shall be Normal as defined in ISO 21111-2.

The initial power state of the LP to measure this time shall be Normal as defined in ISO 21111-2.

#### 5.3.5 IOP\_GEPOF\_REQ\_LINK\_UP\_5

#### REQ 1.7 PHY — IOP\_GEPOF\_REQ\_LINK\_UP\_5

The time measured from the instant when the GEPOF entity 1 receives a WakeUp-request event as specified in ISO 21111-2 till the GEPOF link status in GEPOF entity 1 changes to "bidirectional reliable link is established" shall be lower than 100 ms.

The initial power state of the GEPOF entity 1 to measure this time shall be Normal as defined in ISO 21111-2.

The initial power state of the LP to measure this time shall be Normal as defined in ISO 21111-2.

#### 5.4 Channel quality requirements

#### 5.4.1 IOP\_GEPOF\_REQ\_CH\_QLTY\_1

#### REO 1.8 PHY — IOP\_GEPOF\_REQ\_CH\_QLTY\_1\_(

The GEPOF entity 1 shall indicate the channel quality decrease for a channel with decreasing quality.

#### 5.4.2 IOP\_GEPOF\_REQ\_CH\_QLTY\_2

#### REQ 1.9 PHY — IOP\_GEPOF\_REQ\_CH\_QLTY\_2

The GEPOF entity 1 shall indicate the channel quality increase for a channel with increasing quality.

#### 5.5 Communication reliability under climatic loads requirements

#### 5.5.1 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_1

#### REQ 1.10 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_1

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\rm max}$

- the LP is located in an oven with temperature set to  $T_{\min}$ , and

- the communication channel between them is set as bidirectional high attenuation as specified in REQ 1.20 and REQ 1.21.

#### 5.5.2 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_2

#### REQ 1.11 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_2

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\min}$ ,

- the LP is located in an oven with temperature set to  $T_{\text{max}}$ , and

- the communication channel between them is set as bidirectional high attenuation as specified in REQ 1.20 and REQ 1.21.

#### 5.5.3 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_3

#### REQ 1.12 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_3

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\min}$ ,

- the LP is located in an oven with temperature set to  $T_{\rm m}$  and

- the communication channel between them is set as bidirectional high attenuation as specified in REQ 1.20 and REQ 1.21.

#### 5.5.4 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_4

#### REQ 1.13 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_4

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\rm max}$

- the LP is located in an oven with temperature set to  $T_{\text{max}}$ , and

- the communication channel between them is set as bidirectional high attenuation as specified in REQ 1.20 and REQ 1.21.

#### 5.5.5 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_5

#### REQ 1.14 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_5

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\rm max}$ ,

- the LP is located in an oven with temperature set to  $T_{\min}$ , and

- the communication channel between them is set as bidirectional low attenuation as specified in REQ 1.22 and REQ 1.23.

#### 5.5.6 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_6

#### REQ | 1.15 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_6

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\min}$ ,

- the LP is located in an oven with temperature set to  $T_{\text{max}}$ , and

- the communication channel between them is set as bidirectional low attenuation as specified in REQ 1.22 and REQ 1.23.

#### 5.5.7 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_7

#### REQ 1.16 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_7

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\min}$ ,

- the LP is located in an oven with temperature set to  $T_{\min}$ , and

- the communication channel between them is set as bidirectional low attenuation as specified in REQ 1.22 and REQ 1.23.

#### 5.5.8 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_8

#### REQ 1.17 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_8

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{

m max}$ ,

- the LP is located in an oven with temperature set to  $T_{max}$ , and

- the communication channel between them is set as bidirectional low attenuation as specified in REQ 1.22 and REQ 1.23.

#### 5.5.9 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_9

#### REQ 1.18 PHY IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_9

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\rm device}$

- the LP is located in an oven with temperature set to  $T_{\rm LP}$

- the communication channel between them is set as bidirectional high attenuation as specified in REQ 1.20 and REQ 1.21,

- the initial temperature of  $T_{\text{device}}$  is equal to  $T_{\text{min}}$  and is increased linearly till it reaches  $T_{\text{max}}$  in 30 min, and

- the initial temperature of  $T_{LP}$  is equal to  $T_{max}$  and is decreased linearly till it reaches  $T_{min}$  in 30 min.

#### 5.5.10 IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_10

#### REQ 1.19 PHY — IOP\_GEPOF\_REQ\_RELIABILITY\_TEMP\_10

The communication between GEPOF entity 1 and its LP shall be reliable as specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 when:

- the device that includes the GEPOF entity 1 is located in an oven with temperature set to  $T_{\rm device}$

- the LP is located in an oven with temperature set to  $T_{\rm LP}$ ,

- the communication channel between them is set as bidirectional low attenuation as specified in REQ 1.22 and REQ 1.23,

- the initial temperature of  $T_{\text{device}}$  is equal to  $T_{\text{min}}$  and is increased linearly till it reaches  $T_{\text{max}}$  in 30 min, and

- the initial temperature of  $T_{\rm LP}$  is equal to  $T_{\rm max}$  and is decreased linearly till it reaches  $T_{\rm min}$  in 30 min.

#### 5.6 Test set-up requirements

#### 5.6.1 General

5.6 specifies the requirements of the test set-ups that are used in the interoperability test plan.

Most of the test set-ups involve a communication channel between a device and its LP. Different types of communication channels are specified in <u>5.6</u> and examples of realization are given.

The requirements on the device and LP for the test set-ups are specified in <u>5.6.3</u>.

#### 5.6.2 Channel requirements

#### 5.6.2.1 Bidirectional high attenuation channel

#### 5.6.2.1.1 Bidirectional high attenuation channel requirements

# REQ 1.20 PHY — Bidirectional high attenuation channel requirement — Bidirectional channel structure

The bidirectional high attenuation channel type shall be composed of two unidirectional high attenuation channels. Each of the unidirectional high attenuation channels shall comply with REQ 1.21.

### REQ 1.21 PHY — Bidirectional high attenuation channel requirement — Unidirectional channel requirements

The **un**idirectional high attenuation channel shall have an insertion loss measured at 0 Hz between 6 dB and 7 dB.

The normalized frequency response of the unidirectional high attenuation channel shall be between the normalized frequency response specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 for channel type III and 0,2 dB more for the frequency range from 0 MHz to 162,5 MHz.

The insertion loss and transfer function requirement shall be fulfilled at  $(23 \pm 2)$  °C.

#### 5.6.2.1.2 Example for bidirectional high attenuation channel implementation.

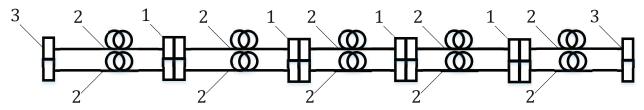

Figure 3 shows an example for a bidirectional high attenuation channel implementation. The simplex POF cable, in-line connector and cable plug fulfil the requirements given in ISO 21111-4. The two-parallel simplex POF cables can be substituted by a single duplex POF cable.

#### Key

- in-line connector 1

- 3-m simplex POF cable 2

- cable plug

Figure 3 — Example for bidirectional high attenuation channel implementation.

Bidirectional low attenuation channel

Bidirectional low attenuation channel requirements

#### 5.6.2.2

#### 5.6.2.2.1

|        | 1.22 PHY — Bidirectional low attenuation channel requirement — Bidirectional channel structure |

|--------|------------------------------------------------------------------------------------------------|

| The hi | directional low attenuation channel type shall be composed of two unidirectional low           |

attenuation channels. Each of the unidirectional low attenuation channels shall comply with REQ 1.23.

#### REO 1.23 PHY — Bidirectional low attenuation channel requirement — Unidirectional channel requirements

The unidirectional low attenuation channel type shall have an insertion loss measured at 0 Hz between 2,5 dB and 3 dB.

The lower limit for transfer function magnitude shall be -0,25 dB for the frequency range from 0 Hz to 160 MHz.

The upper limit for transfer function magnitude shall be 0 dB for the frequency range from 0 Hz to 160 MHz.

The insertion loss and transfer function requirement shall be fulfilled at  $(23 \pm 2)$  °C.

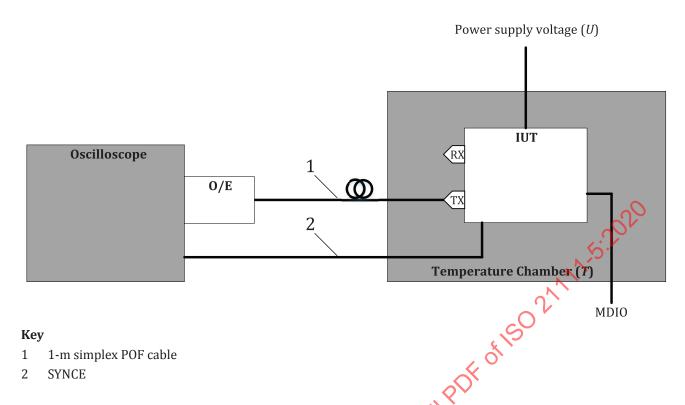

#### 5.6.2.2.2 Example for bidirectional low attenuation channel implementation

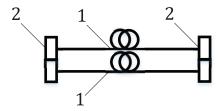

Figure 4 shows an example for a bidirectional low attenuation channel implementation. The simplex POF cable and cable plug fulfil the requirements given in ISO 21111-4. The two-parallel simplex POF cables can be substituted by a single duplex POF cable.

#### Key

- 0,5-m simplex POF cable 1

- cable plug

Figure 4 — Example for bidirectional low attenuation channel implementation

#### 5.6.2.3 Variable attenuation channel

#### **5.6.2.3.1** Variable attenuation channel requirements

### REQ 1.24 PHY — Variable attenuation channel requirements — Bidirectional channel structure

The variable attenuation channel type shall be composed of one unidirectional variable attenuation channel that shall comply with REQ 1.25 and one unidirectional low attenuation channel that shall comply with REQ 1.23.

The unidirectional variable attenuation channel shall connect the upper-left and upper-right ports of the variable attenuation channel.

The unidirectional low attenuation channel shall connect the lower-left and lower-right ports of the variable attenuation channel.

# REQ 1.25 PHY — Variable attenuation channel requirements — Unidirectional channel requirements

The variable attenuation channel type shall have an insertion loss measured at 0 Hz programmable between 3 dB and 10 dB.

The lower limit for transfer function magnitude shall be the requirement specified in ISO/IEC/IEEE 8802-3:2017/Amd 9 for channel type III for the frequency range from 0 Hz to 160 MHz.

The upper limit for transfer function magnitude shall be 0 dB for the frequency range from 0 Hz to 160 MHz.

The insertion loss and transfer function requirement shall be fulfilled at  $(23 \pm 2)$  °C and for all the programmable insertion loss measured at 0 Hz.

#### 5.6.2.3.2 Example for variable attenuation channel implementation

Figure 5 shows an example for a variable attenuation channel implementation. The simplex POF cable and cable plug fulfil the requirements given in ISO 21111-4. Note that the unidirectional variable attenuation channel is implemented only in one communication direction.

#### 5.6.3 Device and LP requirements for interoperability test plan

# REQ 1.26 PHY Device and LP requirements for interoperability test plan — GEPOF entities requirements

Each of the GEPOF entities in the device and LP shall fulfil the requirements in ISO 211113 and ISO/IEC/IEEE 8802-3:2017/Amd 9.

#### REQ 1.27 PHY — Device and LP requirements for interoperability test plan — MDIO interface

The device and the LP shall include at least one accessible MDIO interface as specified in ISO/IEC/IEEE 8802-3 that allows the individual access to each set of MDIO registers of each GEPOF entity in the device or LP.

# REQ 1.28 PHY — Device and LP requirements for interoperability test plan — Access and control of PHY service interface and neighbour service interface

If the device or the LP implements the wake-up and synchronized link sleep functionality as specified in ISO 21111-3, it shall include a way to access and control PHY service interface and neighbour service interface, as specified in ISO 21111-2.

## REQ 1.29 PHY — Device and LP requirements for interoperability test plan — Ethernet interface

The device and the LP shall include at least one Ethernet physical layer capable of 1 Gbit/s in addition to the one provided by the GEPOF entity.

The link status has two possible states:

- "bidirectional reliable link is established" when the MDIO register 1.1 is equal to 12, and

- "bidirectional unreliable link" when the MDIO register 1.1 is equal to  $0_2$ :

# REQ 1.30 PHY — Device and LP requirements for interoperability test plan — Access to link status

The device shall include constant access to the MDIO register 1.1 that contains the current link status.

# REQ 1.31 PHY — Device and LP requirements for interoperability test plan — PMD\_TXPWR.request(tx\_pwr) control

The device and the LP shall include a mechanism to control the generation of the request PMD\_TXPWR.request(tx\_pwr) with a controlled value of the tx\_pwr parameter as specified in ISO/IEEE/IEC 8802-3:2017/Amd 9:2018, 115.6.1.3.

#### Key

- 1 0,5-m simplex POF cable

- 2 cable plug

- 3 optical variable attenuator

- 4 1-m simplex POF cable

Figure 5 — Example for variable attenuation channel implementation

#### 6 Interoperability test plan set-ups

#### 6.1 General

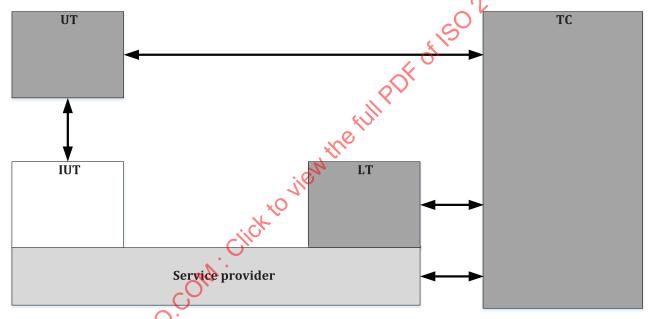

The objective of the interoperability test plan is to verify the physical layer system requirements that need a set-up with at least two GEPOF entities. These test set-ups are relevant for the network system designer.

The IUT for this test plan is the complete network system that includes two or more GEPOF physical entities implemented in, at least, one device and its LP. The interoperability test set-up determines the IUT that is used in each test case.

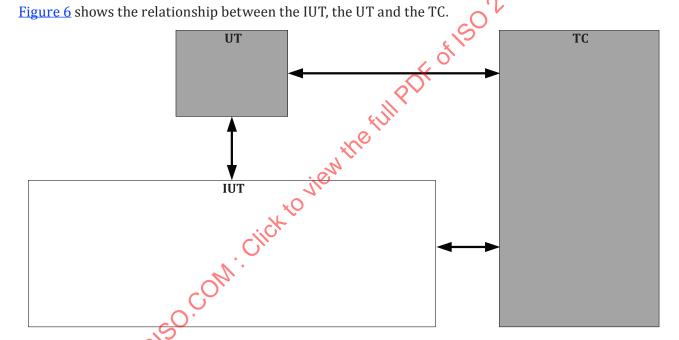

The IUT and the UT are controlled by the TC. The TC implements the functionality of the test coordination procedure specified in ISO/IEC 9646-1.

The IUT has communication with the UT. The UT is able to generate and analyse data from the IUT and check if the result complies with the IUT requirements, as specified in ISO/IEC 9646-1.

Figure 6 — Interoperability test environment

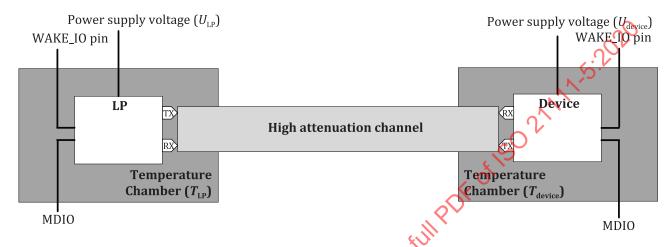

### 6.2 Interoperability test set-up 1

The interoperability test set-up 1 is composed of one device and its LP connected by one bidirectional channel that fulfils the requirements for the bidirectional high attenuation channel type specified in 5.6.2.1.

The device is placed inside a temperature chamber set to a controlled temperature  $T_{\text{device}}$ .

The device is powered by a controlled power supply voltage  $U_{\text{device}}$ .

The LP is placed inside a temperature chamber set to a controlled temperature  $T_{\rm LP}$ .

The LP is powered by a controlled power supply voltage  $U_{\rm LP}$ .

The device, LP1 and LP2 may include a wake I/O block connected to a WAKE\_IO pin as specified in ISO 21111-2:—, 6.6.

#### ISO 21111-5:2020(E)

For the test cases that use this test set-up, to power up the device or LP means to set the power\_off\_ entity variable specified in ISO 21111-2 to FALSE for the GEPOF entity included in the device or LP.

Symmetrically, to power down the device or LP means to set the power\_off\_entity variable specified in ISO 21111-2 to TRUE for the GEPOF entity included in the device or LP.

REQ 1.32 PHY —Interoperability test plan set-ups — Interoperability test set-up 1

The interoperability test setup 1 shall include the elements and the placement specified in Figure 7.

Figure 7 — Interoperability test set-up 1

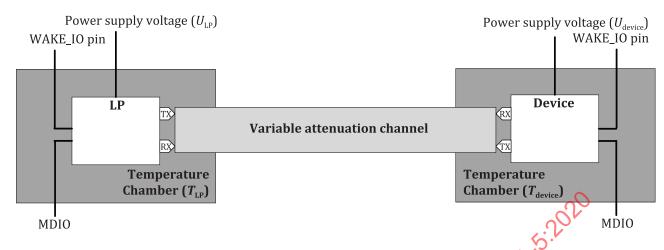

### 6.3 Interoperability test set-up 2

The interoperability test set-up 2 is composed by one device and its LP connected by the variable attenuation channel type specified in 5.6.2.3

The variable attenuation channel implies that the unidirectional channel between the LP transmission and the device reception fulfils REQ 1.25 and that the unidirectional channel between the device transmission and the LP reception fulfils REQ 1.23.

The device is placed inside a temperature chamber set to a controlled temperature  $T_{\text{device}}$ .

The device is powered by a controlled power supply voltage  $U_{\text{device}}$ .

The device, LP1 and LP2 may include a wake I/O block connected to a WAKE\_IO pin as specified in ISO 21111-2:—, 6.6

For the test cases that use this test set-up, to power up the device or LP means to set the power\_off\_ entity variable specified in ISO 21111-2 to FALSE for the GEPOF entity included in the device or LP.

Symmetrically, to power down the device or LP means to set the power\_off\_entity variable specified in ISO 21111-2 to TRUE for the GEPOF entity included in the device or LP.

The LP is placed inside a temperature chamber set to a controlled temperature  $T_{\rm LP}$ .

The LP is powered by a controlled power supply voltage  $U_{LP}$ .

REQ 1.33 PHY — Interoperability test plan set-ups — Interoperability test set-up 2

The interoperability test setup 2 shall include the elements and the placement specified in Figure 8.

Figure 8 — Interoperability test set-up 2

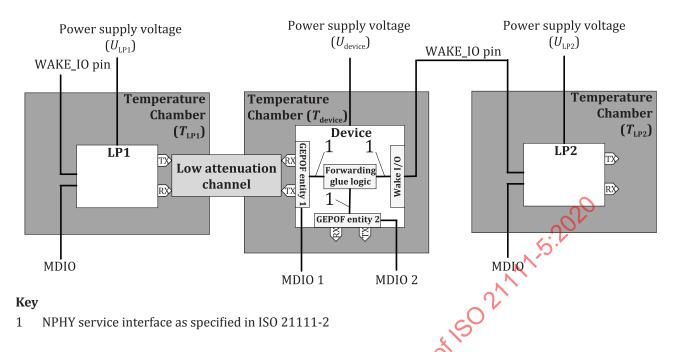

#### 6.4 Interoperability test set-up 3

The interoperability test set-up 3 is composed of one device that includes at least two GEPOF entities and two LPs connected each one with each of the two GEPOF entities in the device by means of two bidirectional channels.

The bidirectional channel between each LP and the device fulfils the requirements for the bidirectional low attenuation channel type specified in <u>5.6.2.2</u>.

The device, LP1 and LP2 may include a wake I/O block connected to a WAKE\_IO pin as specified in ISO 21111-2:—, 6.6.

For the test cases that use this test set-up, to power up the device means to set the power\_off\_entity variable specified in ISO 21111-2 to FALSE for each of the GEPOF entities that are included in the device.

REQ 1.34 PHY — Interoperability test plan set-ups — Interoperability test set-up 3

The interoperability test setup 3 shall include the elements and the placement specified in Figure 9.

Figure 9 \ Interoperability test set-up 3

#### 6.5 Interoperability test set up 4

The interoperability test set-up 4 is composed of one device that includes at least two GEPOF entities and two LPs. One LP is connected with one of the two GEPOF entities in the device by means of a bidirectional channel

The LP1 may include a wake I/O block connected to a WAKE IO pin as specified in ISO 21111-2:—, 6.6.

The device and LP2 include a wake I/O block connected to a WAKE\_IO pin as specified in ISO 21111-2:—, 6.6.

The bidirectional channel between LP1 and the device fulfils the requirements for the bidirectional low attenuation channel type specified in <u>5.6.2.2</u>.

The LP2 is connected to the device by means of the WAKE IO pin specified in ISO 21111-2.

For the test cases that use this test set-up, to power up the device means to set the power\_off\_entity variable specified in ISO 21111-2 to FALSE for each of the GEPOF entities that are included in the device.

REQ 1.35 PHY — Interoperability test plan set-ups — Interoperability test set-up 4

The interoperability test setup 4 shall include the elements and the placement specified in Figure 10.

Figure 10 — Interoperability test set-up 4

### 7 Interoperability test plan

#### 7.1 General

The interoperability test plan is a set of test cases that checks system network requirements and needs a test set-up with at least one GEPOF entity and its LP. This test plan is relevant for system network designers.

This test plan is structured in test groups. The test cases in the same test group share the same test set-up.

The interoperability test cases which require variations of individual parameters, shall be repeated for each value of the parameter.

The interoperability test case specifications are intended to provide a high-level description of the motivation, resources, procedures, and methodologies pertinent to each test case. Each interoperability test case is specified according to a common structure as shown in <u>Table 1</u>.

| Item           | Content                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number - Title | 1 - Test case structure                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Purpose        | The purpose is a brief statement outlining what the test case attempts are to achieve. The test case is written at the functional level.                                                                                                                                                                                                                                                                     |  |

| Reference      | The purpose of reference is to specify source material external to the test plan, including any other references that might be helpful in understanding the test methodology and/ or test case results. External sources are always referenced by number when mentioned in the test case description. Any other references not specified by number are stated with respect to the test plan document itself. |  |

| Prerequisite   | The purpose of prerequisites is to specify the test case hardware and/or software needed to perform the test case. This is generally expressed in terms of minimum requirements. In                                                                                                                                                                                                                          |  |

some cases, specific equipment manufacturer/model information may be provided.

Table 1 — Test case structure

Table 1 (continued)

| Item              | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Set-up            | The purpose of set-up is to describe the initial configuration of the test case environment. Small changes in the configuration should not be included here and are generally covered in the test step section below.                                                                                                                                                                                                                                    |  |

| Step              | The test case steps include the test case description, which contains the systematic instructions for carrying out the test case. It provides a cookbook approach to testing and may be interspersed with observable results. Each test case step shall have a numeric number in ascending order.                                                                                                                                                        |  |

| Iterations        | The purpose of test case iterations is to include test procedure definitions, which are repeated more than once.                                                                                                                                                                                                                                                                                                                                         |  |

| Expected response | The purpose of expected response is to describe the expected results to be examined by the test person in order to verify that the test case is operating. When multiple values for an observable are possible, this description provides a short discussion on how to interpret them. The determination of a pass or fail outcome for a particular test case is generally based on the successful (or unsuccessful) detection of a specific observable. |  |

| Remark            | The purpose of remark is to describe known issues with the test case steps, which can affect test results in certain situations. It can also refer the reader to test plan annexes and/or white papers that can provide more detail regarding these issues.                                                                                                                                                                                              |  |

Some of the test cases refer to different values of the climatic chamber temperature T and different values of the voltage U that is supplied to the device and to the LP.

| REQ     | 1.36 PHY — Interoperability test plan — Temperature and voltage values                                                                              |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The ty  | pical, minimum, and maximum values $T_{ m typ}$ , $T_{ m min}$ , $T_{ m max}$ , $U_{ m typ}$ , $U_{ m min}$ , and $U_{ m max}$ shall be provided by |  |

| the tes | the test person.                                                                                                                                    |  |

### 7.2 High attenuation channel with climatic load

<u>Table 2</u> specifies the interoperability test case <u>NTC\_01\_link-up\_1\_device\_sleep</u> for the high attenuation channel specified in <u>5.6.2.1</u>.

Table 2 — 1.ITC\_01\_link-up\_1\_device\_sleep — High attenuation channel with climatic load

| Item           | Content                                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number - Title | 1.ITC_01_link-up_1_device_sleep — Link-up time when device is in sleep power state under high attenuation channel                                                                                                                                            |

| Purpose        | This test case determines the link-up time from reset when the device is in sleep power state in a controlled network system at typical temperature and power supply voltage.  The test case verifies that the calculated link up time is lower than 100 ms. |

| Reference      | SO 21111-3:2020, 6.4, REQ 1.5.                                                                                                                                                                                                                               |

| Prerequisites  | Device shall provide access to the interfaces specified in <u>5.6.3</u> .                                                                                                                                                                                    |

| Set-up         | 6.2 - Interoperability test set-up 1.                                                                                                                                                                                                                        |

Table 2 (continued)

| Item              | Content                                                                                                                                                   |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number - Title    | 1.ITC_01_link-up_1_device_sleep — Link-up time when device is in sleep power state under high attenuation channel                                         |  |  |

| Step              | 1. The TC shall set the device climatic chamber temperature $T_{ m device}$ to $T_{ m typ}$ .                                                             |  |  |

|                   | 2. The TC shall set the device power supply voltage $U_{ m device}$ to $U_{ m typ}$ .                                                                     |  |  |

|                   | 3. The TC shall set the LP climatic chamber temperature $T_{\rm LP}$ to $T_{\rm typ}$ .                                                                   |  |  |

|                   | 4. The TC shall set the LP power supply voltage $U_{\mathrm{LP}}$ to $U_{\mathrm{typ}}$ .                                                                 |  |  |

|                   | <ul> <li>5. The TC shall power up the LP.</li> <li>6. The TC shall power up the device.</li> <li>7. The TC shall wait 100 ms.</li> </ul>                  |  |  |

|                   | 6. The TC shall power up the device.                                                                                                                      |  |  |

|                   | 7. The TC shall wait 100 ms.                                                                                                                              |  |  |

|                   | The UT shall write the device MDIO register bit 15 of the MDIO register 1.0 with $1_2$ . Then the TC shall reset to zero the T_LINKUP timer and start it. |  |  |

|                   | . The TC shall wait till the device MDIO register bit 15 of the MDIO register 1.0 is equal to $\theta_2$ .                                                |  |  |

|                   | 10. The UT shall get the device link status at least once each millisecond.                                                                               |  |  |

|                   | 11. When the device link status is equal to "bidirectional reliable link is established", the TC shall stop the T_LINKUP timer.                           |  |  |

|                   | 12. The TC shall check that the value in the T_LINKUP timer is lower than 100 ms.                                                                         |  |  |

| Iterations        | N/A                                                                                                                                                       |  |  |

| Expected response | Result of check in step 12 is OK.                                                                                                                         |  |  |

| Remarks           | N/A , CF                                                                                                                                                  |  |  |

<u>Table 3</u> specifies the interoperability test case 1.ITC\_02\_link-up\_2\_LP\_sleep for the high attenuation channel specified in <u>5.6.2.1</u>.

Table 3 — 1.ITC\_02\_link-up\_2\_LP\_sleep — High attenuation channel with climatic load

| Item           | Content                                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number - Title | 1.ITC_02_link-up_2_LP_sleep — Link-up time when LP is in sleep power state under high attenuation channel                                                                                                                                    |

| Purpose        | This test case determines the link-up time when the LP is in sleep power state in a controlled network system at typical temperature and power supply voltage. The test case verifies that the calculated link up time is lower than 100 ms. |

| Reference      | ISO 21111-3:2020, 6.4, REQ 1.6.                                                                                                                                                                                                              |

| Prerequisites  | Device shall provide access to the interfaces specified in <u>5.6.3</u> .                                                                                                                                                                    |

| Set-up         | 6.2 - Interoperability test set-up 1.                                                                                                                                                                                                        |

Table 3 (continued)

| Item           | Content                                                                                                                                                                                                                  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number – Title | 1.ITC_02_link-up_2_LP_sleep — Link-up time when LP is in sleep power state under high attenuation channel                                                                                                                |  |  |

| Step           | 1. The TC shall set the device climatic chamber temperature $T_{ m device}$ to $T_{ m typ}$ .                                                                                                                            |  |  |

|                | 2. The TC shall set the device power supply voltage $U_{ m device}$ to $U_{ m typ}$ .                                                                                                                                    |  |  |