## INTERNATIONAL **STANDARD**

# ISO/ **IEC/IEEE** 8802-3

Third edition 2021-02

**AMENDMENT 3**

Telecommunications and exchange between information technology systems — Requirements for local and metropolitan area networks —

### Part 3: Standard for Ethernet

AMENDMENT 3: Media access control parameters for 50 Gb/s and physical layers and management parameters for 50 Gb/s, 100 Gb/s, and 200 Gb/s operation

Télécommunications et échange entre systèmes informatiques — Exigences pour les réseaux locaux et métropolitains —

Partie 3: Norme pour Ethernet

ECHORIN. Click to view AMENDEMENT 3: Paramètres de commande d'accès media pour 50 Gb/s et couches physiques et paramètres de gestion pour fonctionnement à 50 Gb/s, 100 Gb/s et 200 Gb/s

Reference number ISO/IEC/IEEE 8802-3:2021/Amd.3:2021(E)

#### **COPYRIGHT PROTECTED DOCUMENT**

© IEEE 2019

All rights reserved. Unless otherwise specified, or required in the context of its implementation, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from IEEE at the address below.

Institute of Electrical and Electronics Engineers, Inc 3 Park Avenue, New York NY 10016-5997, USA

Email: stds.ipr@ieee.org Website: www.ieee.org Published in Switzerland

#### Foreword

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular, the different approval criteria needed for the different types of ISO/IEC documents should be noted.

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see <a href="www.iso.org/patents">www.iso.org/patents</a>) or the IEC list of patent declarations received (see <a href="patents.iec.ch">patents.iec.ch</a>).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation of the voluntary nature of standards, the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT), see <a href="https://www.iso.org/iso/foreword.html">www.iso.org/iso/foreword.html</a>. In the IEC, see <a href="https://www.iec.ch/understanding-standards">www.iec.ch/understanding-standards</a>.

ISO/IEC/IEEE 8802-3:2021/Amd.3 was prepared by the LAN/MAN of the IEEE Computer Society (as IEEE Std 802.3cd-2018) and drafted in accordance with its editorial rules. It was adopted, under the "fast-track procedure" defined in the Partner Standards Development Organization cooperation agreement between ISO and IEEE, by Joint Technical Committee ISO/IEC JTC 1, *Information technology*, Subcommittee SC 6, *Telecommunications and information exchange between systems*.

A list of all parts in the ISO/IEC/IEEE 8802 series can be found on the ISO and IEC websites.

Any feedback or questions on this document should be directed to the user's national standards body. A complete listing of these bodies can be found at <a href="www.iso.org/members.html">www.iso.org/members.html</a> and <a href="www.iec.ch/national-committees">www.iec.ch/national-committees</a>.

ECNORM.COM. Click's view the full POF of SOILECHELE 8807.3:2021 Hand 3:2021

#### IEEE Std 802.3cd™-2018

(Amendment to IEEE Std 802.3™-2018 as amended by IEEE Std 802.3cb™-2018 and IEEE Std 802.3bt™-2018)

### **IEEE Standard for Ethernet**

**Amendment 3:** Media Access Control Parameters for 50 Gb/s and Physical Layers and Management Parameters for 50 Gb/s, 100 Gb/s, and 200 Gb/s Operation

Sponsor

LAN/MAN Standards Committee relationship of the IEEE Computer Society

Approved

Approved 5 December 2018

ECHORNI. COM. **IEEE-SA Standards Board**  Abstract: Clause 131 through Clause 140 and Annex 135A through Annex 136D are added to IEEE Std 802.3-2018 by this amendment to specify IEEE 802.3 Media Access Control (MAC) parameters, Physical Layer specifications, and management parameters for the transfer of IEEE 802.3 format frames at 50 Gb/s, 100 Gb/s, and 200 Gb/s.

Keywords: 50GAUI-1, 50GAUI-2, 50GBASE-CR, 50GBASE-FR, 50GBASE-KR, 50GBASE-LR, 50GBASE-SR, 50 Gigabit Ethernet, 50GMII, 100GAUI-2, 100GAUI-4, 100GBASE-CR2, -CF -Efficie JI-2, MMI JI-2, MMI AM. Click to view the full patr of ESOILECILIFIE 8807.33.702 view the full patr of ESOILECILI 100GBASE-DR, 100GBASE-KR2, 100GBASE-SR2, 100 Gigabit Ethernet, 200GBASE-CR4, 200GBASE-KR4, 200GBASE-SR4, 200 Gigabit Ethernet, amendment, EEE, Energy-Efficient Ethernet, Ethernet, FEC, forward error correction, IEEE 802.3™, IEEE 802.3cd™, LAUI-2, MMF,⊃ **SMF**

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2019 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 15 February 2019. Printed in the United States of America.

IEEE and 802 are registered trademarks in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-1-5044-5357-8 STD23441 ISBN 978-1-5044-5358-5 STDPD23441

IEEE prohibits discrimination, harassment and bullying.

For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission

# Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notices and Disclaimers Concerning IEEE Standards Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/ipr/disclaimers.html">http://standards.ieee.org/ipr/disclaimers.html</a>.

# Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (\*IEEE-SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE Standards are documents developed through scientific, academic, and industry-based technical working groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers and users of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

#### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

#### Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is of ISOIR CIREPE welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

#### Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

#### **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

#### **Updating of IEEE Standards documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at <a href="http://ieeexplore.ieee.org">http://ieeexplore.ieee.org</a> or contact IEEE at the address listed previously. For more information about the IEEE SA or IEEE's standards development process, visit the IEEE-SA Website at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: <a href="http://standards.ieee.org/findstds/errata/index.html">http://standards.ieee.org/findstds/errata/index.html</a>. Users are encouraged to check this URL for errata periodically.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at <a href="http://standards.ieee.org/about/sasb/patcom/patents.html">http://standards.ieee.org/about/sasb/patcom/patents.html</a> Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

#### **Participants**

The following individuals were officers and members of the IEEE 802.3 Working Group at the beginning of the IEEE P802.3cd Working Group ballot.

> 2:3:2021Amd3:2021 David J. Law, IEEE 802.3 Working Group Chair Adam Healey, IEEE 802.3 Working Group Vice-Chair **Pete Anslow,** *IEEE 802.3 Working Group Secretary* Steven B. Carlson, IEEE 802.3 Working Group Executive Secretary Valerie Maguire, IEEE 802.3 Working Group Treasurer

Mark Nowell, IEEE P802.3cd Task Force Chair Matt Brown, IEEE P802.3cd Task Force Editor-in-Chief **Arthur Marris**, IEEE P802.3cd Task Force Editor Gary Nicholl, IEEE P802.3cd Task Force Editor Adee Ran, IEEE P802.3cd Task Force Editor **Jonathan King**, <sup>1</sup> *IEEE P802.3cd Task Force Editor* Peter Stassar, IEEE P802.3cd Task Force Editor

Justin Abbott David Abramson Dale Amason Eric Baden Amrik Bains Thananya Baldwin Denis Beaudoin Christian Beia Vipul Bhatt William Bliss Mark Bohm **Brad Booth** Martin Bouda David Brandt Ralf-Peter Braun Theodore Brillhart Paul Brooks Phillip Brownlee Chris Bullock

Jairo Bustos Heredia

Anthony Calbone

Adrian Butter

Clark Carty Craig Chabot Mandeep Chadha David Chalupsky Jacky Chang Xin Chang Chan Chen Weiying Cheng Golam Choudhury Keng Hua Chuang Christopher R. Cole John D'Ambrosia Piers J. G. Dawe Fred Dawson

Eric DiBiaso John Dillard Chris Diminico Curtis Donahue Michael Dudek Frank Effenberger John Ewen Ramin Farjad Shahar Feldman Matthias Fritsche Richard Frosch Andrew Gardner Ali Ghiasi Steven Gorshe Steffen Graber Olaf Grau Robert M. Grow Yong Guo Mark Gustlin Marek Hajduczenia Tomohiro Hashimoto Akinori Hayakawa Raimohan Hegde David Hess Yasuo Hidaka David Hoglund Rita Horner Bernd Horrmeyer Xi Huang Xingang Huang Yasuhiro Hyakutake

John Johnson Chad Jones Peter Jones Upen Kareti Yasuaki Kawatsu Yongbum Kim Mark Kimber Scott Kipp Michael Klempa Curtis Knittle Shigeru Kobayashi Paul Kolesar Toshihiko Kusano Hans Lackner Jeffrey Lapak Mark Laubach Greg Le Cheminant Hanan Leizerovich David Lewis Jon Lewis Mike Peng Li Robert Lingle Hai-Feng Liu Zhenvu Liu Moiz Lokhandwala Miklos Lukacs Kent Lusted Zahy Madgar Jeffery Maki David Malicoat Takeo Masuda Kirsten Matheus Erdem Matoglu

Andrew Jimenez

Jonathan Ingham

Kazuhiko Ishibe

Hideki Isono

Tom Issenhuth

Kenneth Jackson

<sup>&</sup>lt;sup>1</sup>Not a member of the IEEE 802.3 working group at the beginning of the working group ballot.

Mick McCarthy Brett McClellan Thomas McDermott John McDonough Larry McMillan Greg McSorley Marcel Medina Richard Mei Richard Mellitz Phil Miguelez Paul Mooney Ron Muir Dale Murray

Henry Muyshondt Edward Nakamoto Kevin Noll David Ofelt Thomas Palkert Sujan Pandey Sesha Panguluri Earl Parsons Wanquan Peng

Ruben Perez De Aranda Alonso

Michael Peters Jean Picard David Piehler Rick Pimpinella William Powell Rick Rabinovich

Alon Regev Duane Remein Salvatore Rotolo Sam Sambasivan **Edward Savre** Fred Schindler Masood Shariff Kapil Shrikhande Jeff Slavick Daniel Smith Scott Sommers Yoshiaki Sone Bryan Sparrowhawk Atul Srivastava Heath Stewart David Stover Ken-Ichi Suzuki

Andre Szczepanek William Szeto **Bharat Tailor** Takavuki Taiima Tomoo Takahara Kohichi Tamura Nathan Tracy Matthew Traverso David Tremblay Stephen Trowbridge

Steve Swanson

Yoshihiro Tsukamoto Ed Ulrichs Alexander Umnov Sterling A. Vaden Stefano Valle Paul Vanderlaan Dylan Walker Roy Wang Tongtong Wang Xinyuan Wang Matthias Wendt Oded Wertheim Natalie Wienckowsk

Ludwig Winkel

Peter Wu

Dayin Xu Yu Xu Lennart Yseboodt Hayato Yuki Andrew Zambell Huanlin Zhang Oiwen Zhong Yan Zhuang George Zimmerman Helge Zinner Pavel Zivny

Hyeong Ho Lee

The following members of the individual balloting committee voted on this amendment. Balloters may have voted for approval, disapproval, or abstention.

Brian Franchuk

Thomas Alexander Richard Alfvin Arne Alping Pete Anslow **Butch Anton** Eric Baden John Ballingall Ralf-Peter Braun Nancy Bravin Theodore Brillhart Matt Brown Demetrio Bucaneg Gary Burrell Jairo Bustos Heredia William Byrd John Calvin Steven B. Carlson Juan Carreon Clark Carty Chan Chen Keith Chow Keng Hua Chuang Charles Cook Piers J. G. Dawe Stephen Didde Michael Dudek

Sourav Dutta

Jason Ellison

Avraham Freedman Yukihiro Fujimoto Zhigang Gong Eric W. Gray Randall Groves Mark Gustlin Adam Healey Marco Hernandez David Hess Yasuo Hidaka Werner Hoelzl Rita Horner Noriyuki Ikeuchi Sergiu Iordanescu Osamu Ishida Atsushi Ito Rai Jain SangKwon Jeong Peter Jones Manabu Kagami Piotr Karocki Stuart Kerry Yongbum Kim Jonathan King Paul Kolesar Mark Laubach David J. Law

Hanan Leizerovich David Lewis Jon Lewis Robert Lingle Hai-Feng Liu Kent Lusted Michael Lynch Elvis Maculuba Valerie Maguire Jeffery Maki Arthur Marris Michael Maytum Mick McCarthy Brett McClellan Thomas McDermott Richard Mellitz Tremont Miao Charles Moorwood Rick Murphy Michael Newman Charles Ngethe Gary Nicholl Nick S. A. Nikjoo Mark Nowell Satoshi Obara Thomas Palkert Bansi Patel

| Arumugam Paventhan |

|--------------------|

| Michael Peters     |

| David Piehler      |

| Rick Pimpinella    |

| Adee Ran           |

| R. K. Rannow       |

| Alon Regev         |

| Maximilian Riegel  |

| Robert Robinson    |

| Alexander Rysin    |

| Toshiaki Sakai     |

| Kapil Shrikhande   |

| Jason Shriver      |

| Jeff Slavick       |

| Daniel Smith       |

| Thomas Starai      |

Peter Stassar Robert Stone Walter Struppler Mitsutoshi Sugawara Junqing Sun Patrik Sundstrom Andre Szczepanek Kohichi Tamura David Thompson Geoffrey Thompson Michael Thompson David Tremblay Stephen Trowbridge Mark-Rene Uchida Alexander Umnov Paul Vanderlaan

Dmitri Varsanofiev George Vlantis Khurram Waheed Lisa Ward Keith Waters Oded Wertheim Andreas Wolf Chun Yu Charles Wong

Peter Wu Xin Wu Jun Xu Adrian Young Oren Yuen Andrew Zambell Zhen Zhou Pavel Zivny

When the IEEE-SA Standards Board approved this amendment on 5 December 2018, it had the following membership:

> Jean-Philippe Faure, Chair Gary Hoffman, Vice Chair John D. Kulick, Past Chair Konstantinos Karachalios, Segretary

Ted Burse Guido R. Hiertz Christel Hunter Joseph L. Koepfinger\* Thomas Koshy ECNORM. COM. Circk to view the full Hung Ling

Xiaohui Liu Kevin Lu Daleep Mohla Andrew Myles Paul Nikolich Ronald C. Petersen Annette D. Reilly

Robby Robson Dorothy Stanley Mehmet Ulema Phil Wennblom Philip Winston Howard Wolfman Jingyi Zhou

#### Introduction

This introduction is not part of IEEE Std 802.3cd-2018, IEEE Standard for Ethernet. Amendment 3: Media Access Control Parameters for 50 Gb/s and Physical Layers and Management Parameters for 50 Gb/s, 100 Gb/s, and 200 Gb/s Operation.

IEEE Std 802.3<sup>™</sup> was first published in 1985. Since the initial publication, many projects have added functionality or provided maintenance updates to the specifications and text included in the standard. Each IEEE 802.3 project/amendment is identified with a suffix (e.g., IEEE Std 802.3ba<sup>™</sup>-2010).

The half duplex Media Access Control (MAC) protocol specified in IEEE Std 802.3-1985 is Carrier Sense Multiple Access with Collision Detection (CSMA/CD). This MAC protocol was key to the experimental Ethernet developed at Xerox Palo Alto Research Center, which had a 2.94 Mb/s data rate. Ethernet at 10 Mb/s was jointly released as a public specification by Digital Equipment Corporation (DEC), Intel and Xerox in 1980. Ethernet at 10 Mb/s was approved as an IEEE standard by the IEEE Standards Board in 1983 and subsequently published in 1985 as IEEE Std 802.3-1985. Since 1985, new media options, new speeds of operation, and new capabilities have been added to IEEE Std 802.3. A full duplex MAC protocol was added in 1997.

Some of the major additions to IEEE Std 802.3 are identified in the marketplace with their project number. This is most common for projects adding higher speeds of operation or new protocols. For example, IEEE Std 802.3u<sup>TM</sup> added 100 Mb/s operation (also called Fast Ethernet), IEEE Std 802.3z added 1000 Mb/s operation (also called Gigabit Ethernet), IEEE Std 802.3ae added 10 Gb/s operation (also called 10 Gigabit Ethernet), IEEE Std 802.3ah<sup>TM</sup> specified access network Ethernet (also called Ethernet in the First Mile) and IEEE Std 802.3ba added 40 Gb/s operation (also called 40 Gigabit Ethernet). These major additions are all now included in and are superseded by IEEE Std 802.3-2018 and are not maintained as separate documents.

At the date of publication for IEEE Std 802.3cd-2018, IEEE Std 802.3 was composed of the following documents:

IEEE Std 802.3-2018

Section One—Includes Clause 1 through Clause 20 and Annex A through Annex H and Annex 4A. Section One includes the specifications for 10 Mb/s operation and the MAC, frame formats and service interfaces used for all speeds of operation.

Section Two—Includes Clause 21 through Clause 33 and Annex 22A through Annex 33E. Section Two includes management attributes for multiple protocols and speed of operation as well as specifications for providing power over twisted pair cabling for multiple operational speeds. It also includes general information on 100 Mb/s operation as well as most of the 100 Mb/s Physical Layer specifications.

Section Three—Includes Clause 34 through Clause 43 and Annex 36A through Annex 43C. Section Three includes general information on 1000 Mb/s operation as well as most of the 1000 Mb/s Physical Layer specifications.

Section Four—Includes Clause 44 through Clause 55 and Annex 44A through Annex 55B. Section Four includes general information on 10 Gb/s operation as well as most of the 10 Gb/s Physical Layer specifications.

Section Five—Includes Clause 56 through Clause 77 and Annex 57A through Annex 76A. Clause 56 through Clause 67 and Clause 75 through Clause 77, as well as associated annexes, specify subscriber

access and other Physical Layers and sublayers for operation from 512 kb/s to 10 Gb/s, and defines services and protocol elements that enable the exchange of IEEE Std 802.3 format frames between stations in a subscriber access network. Clause 68 specifies a 10 Gb/s Physical Layer specification. Clause 69 through Clause 74 and associated annexes specify Ethernet operation over electrical backplanes at speeds of 1000 Mb/s and 10 Gb/s.

Section Six—Includes Clause 78 through Clause 95 and Annex 83A through Annex 93C. Clause 78 specifies Energy-Efficient Ethernet. Clause 79 specifies IEEE 802.3 Organizationally Specific Link Layer Discovery Protocol (LLDP) type, length, and value (TLV) information elements. Clause 80 through Clause 95 and associated annexes include general information on 40 Gb/s and 100 Gb/s operation as well as 40 Gb/s and 100 Gb/s Physical Layer specifications. Clause 90 specifies Ethernet support for time synchronization protocols.

Section Seven—Includes Clause 96 through Clause 115 and Annex 97A through Annex 115A. Clause 96 through Clause 98, Clause 104, and associated annexes, specify Physical Layers and optional features for 100 Mb/s and 1000 Mb/s operation over a single twisted pair. Clause 100 through Clause 103, as well as associated annexes, specify Physical Layers for the operation of the EPON protocol over coaxial distribution networks. Clause 105 through Clause 114 and associated annexes include general information on 25 Gb/s operation as well as 25 Gb/s Physical Layer specifications. Clause 99 specifies a MAC merge sublayer for the interspersing of express traffic. Clause 115 and its associated annex specify a Physical Layer for 1000 Mb/s operation over plastic optical fiber.

Section Eight—Includes Clause 116 through Clause 126 and Annex 119A through Annex 120E. Clause 116 through Clause 124 and associated annexes include general information on 200 Gb/s and 400 Gb/s operation as well the 200 Gb/s and 400 Gb/s Physical Layer specifications. Clause 125 and Clause 126 include general information on 2.5 Gb/s and 5 Gb/s operation as well as 2.5 Gb/s and 5 Gb/s Physical Layer specifications.

#### IEEE Std 802.3cb-2018

Amendment 1—This amendment includes changes to IEEE Std 802.3-2018 and its amendments, and adds Clause 127 through Clause 130, Annex 127A, Annex 128A, Annex 128B, Annex 128C, and Annex 130A. This amendment adds new Physical Layers for operation at 2.5 Gb/s and 5 Gb/s over electrical backplanes.

#### IEEE Std 802.3bt-2018

Amendment 2—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 145, Annex 145A, Annex 145B, and Annex 145C. This amendment adds power delivery using all four pairs in the structured wiring plant, resulting in greater power being available to end devices. This amendment also allows for lower standby power consumption in end devices and adds a mechanism to better manage the available power budget.

#### IEEE Std 802.3cd™-2018

Amendment 3—This amendment includes changes to IEEE Std 802.3-2018 and adds Clause 131 through Clause 140 and Annex 135A through Annex 136D. This amendment adds MAC parameters, Physical Layers, and management parameters for the transfer of IEEE 802.3 format frames at 50 Gb/s, 100 Gb/s, and 200 Gb/s.

A companion document, IEEE Std 802.3.1, describes Ethernet management information base (MIB) modules for use with the Simple Network Management Protocol (SNMP). IEEE Std 802.3.1 is updated to add management capability for enhancements to IEEE Std 802.3 after approval of those enhancements.

IEEE Std 802.3 will continue to evolve. New Ethernet capabilities are anticipated to be added within the

ECHCEM.COM. Clicke view the full POF of SOMECHEEL 8897.3: 2021 HAND 3:2021

#### Contents

| 1. Introduction                                          | 35  |

|----------------------------------------------------------|-----|

| 1.1 Overview                                             | 35  |

| 1.1.3 Architectural perspectives.                        |     |

| 1.1.3.2 Compatibility interfaces                         | 35  |

| 1.3 Normative references                                 |     |

| 1.4 Definitions                                          | 36  |

| 1.5 Abbreviations                                        | 375 |

| 4. Media Access Control                                  | 38  |

| 4.4 Specific implementations 4.4.2 MAC parameters        | 38  |

| 4.4.2 MAC parameters                                     | 38  |

| γ····                                                    |     |

| 30. Management                                           |     |

|                                                          |     |

| 30.3 Layer management for DTEs                           | 39  |

| 30.3.2 PHY device managed object class                   | 39  |

|                                                          |     |

| 30.3.2.1.2 aPhyType 30.3.2.1.3 aPhyTypeList              | 39  |

| 30.3.2.1.3 aPhyTypeList                                  | 39  |

| 30.3.2.1.5 aSymbolErrorDuringCarrier                     | 39  |

| 30.5 Layer management for medium attachment units (MALk) | 39  |

| 30.5.1 MAU managed object class                          | 39  |

| 30.5.1.1 MAU attributes                                  | 39  |

| 30.5.1.1.2 aMAUType                                      | 39  |

| 30.5.1.1.4 aMediaAvailable                               | 40  |

| 30.5.1.1.11 aBIPErrorCount                               | 41  |

| 30.5.1.1.12 aLaneMapping                                 |     |

| 30.5.1.1.17 aFECCorrected Blocks                         |     |

| 30.5.1.1.18 aFECUncorrectableBlocks                      |     |

| 30.5.1.1.26 aRSFEGBIPErrorCount                          |     |

| 30.5.1.1.27 aRSFECLaneMapping                            |     |

| 30.5.1.1.29 aRSFECBypassIndicationAbility                |     |

| 30.5.1.1.31 aRSFECBypassIndicationEnable                 |     |

| 30.6 Management for link Auto-Negotiation                |     |

| 30.6.1 Auto-Negotiation managed object class             |     |

| 30.6.1.1 Auto-Negotiation attributes                     |     |

| 30.6.1.1.5 aAutoNegLocalTechnologyAbility                | 43  |

| 45. Management Data Input/Output (MDIO) Interface        | 44  |

| 45.2 MDIO Interface Registers                            | 11  |

| 45.2.1 PMA/PMD registers                                 |     |

| 45.2.1 PMA/PMD registers (Register 1.0)                  |     |

| 45.2.1.1.3 Speed selection (1.0.13, 1.0.6, 1.0.5:2)      |     |

| 45.2.1.2 PMA/PMD status 1 register (Register 1.1)        |     |

| 45.2.1.2.3 Fault (1.1.7)                                 |     |

| 45.2.1.4 PMA/PMD speed ability (Register 1.4)            |     |

| 45.2.1.4.12a 50G capable (1.4.3)                         |     |

| 45.2.1.6 PMA/PMD control 2 register (Register 1.7)       |     |

| 45.2.1.6.3 PMA/PMD type selection (1.7.6:0)              | 48  |

| 45.2.1.7 PMA/PMD status 2 register (Register 1.8)                                                                                                                                                                                                                       | 48 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 45.2.1.7.4 Transmit fault (1.8.11)                                                                                                                                                                                                                                      | 48 |

| 45.2.1.7.5 Receive fault (1.8.10)                                                                                                                                                                                                                                       |    |

| 45.2.1.8 PMD transmit disable register (Register 1.9)                                                                                                                                                                                                                   |    |

| 45.2.1.17a 50G PMA/PMD extended ability (Register 1.20)                                                                                                                                                                                                                 |    |

| 45.2.1.17a.1 50G PMA remote loopback ability (1.20.15)                                                                                                                                                                                                                  |    |

| 45.2.1.17a.2 50GBASE-LR ability (1.20.4)                                                                                                                                                                                                                                |    |

| 45.2.1.17a.3 50GBASE-FR ability (1.20.3)                                                                                                                                                                                                                                |    |

| 45.2.1.17a.4 50GBASE-SR ability (1.20.2)                                                                                                                                                                                                                                |    |

| 45.2.1.17a.5 50GBASE-CR ability (1.20.1)                                                                                                                                                                                                                                |    |

| 45.2.1.17a.6.50GBASE KR ability (1.20.1)                                                                                                                                                                                                                                | 31 |

| 45.2.1.17a.6 50GBASE-KR ability (1.20.0)                                                                                                                                                                                                                                | 51 |

| 45.2.1.21a FIVIA/FIVID extended abilities (1.25.0)                                                                                                                                                                                                                      | 51 |

| 45.2.1.218.1 500 extended abilities (1.25.0)                                                                                                                                                                                                                            | 51 |

| 45.2.1.89 BASE-R PMD control register (Register 1.150) 45.2.1.90 BASE-R PMD status register (Register 1.151) 45.2.1.90.1 Receiver status 0 (1.151.0)                                                                                                                    | 52 |

| 45.2.1.90 BASE-R PMD status register (Register 1.151)                                                                                                                                                                                                                   | 52 |

| 45.2.1.90.1 Receiver status 0 (1.151.0)                                                                                                                                                                                                                                 | 52 |

| 45.2.1.90.2 Frame lock 0 (1.151.1)                                                                                                                                                                                                                                      | 52 |

| 45.2.1.90.1 Receiver status 0 (1.151.0) 45.2.1.90.2 Frame lock 0 (1.151.1) 45.2.1.90.3 Start-up protocol status 0 (1.151.2) 45.2.1.90.4 Training failure 0 (1.151.3) 45.2.1.110 RS-FEC control register (Register 1.200) 45.2.1.110 a FEC degraded SER enable (1.200.4) | 52 |

| 45.2.1.90.4 Training failure 0 (1.151.3)                                                                                                                                                                                                                                | 52 |

| 45.2.1.110 RS-FEC control register (Register 1.200)                                                                                                                                                                                                                     | 53 |

|                                                                                                                                                                                                                                                                         |    |

| 45.2.1.110.b Four-lane PMD (1.200.3)                                                                                                                                                                                                                                    | 53 |

| 45.2.1.110.2 FEC bypass indication enable (1.200.1)                                                                                                                                                                                                                     | 54 |

| 45.2.1.111 RS-FEC status register (Register 1.201)                                                                                                                                                                                                                      | 54 |

| 45.2.1.111.1 PCS align status (1.201.15)                                                                                                                                                                                                                                | 54 |

| 45.2.1.111.2.RS-FFC align status (1.201.14)                                                                                                                                                                                                                             | 54 |

| 45.2.1.111.5 FEC AM lock 1 (1.201.9)                                                                                                                                                                                                                                    | 55 |

| 45.2.1.111.6 FEC AM lock 0 (1.201.8)                                                                                                                                                                                                                                    | 55 |

| 45.2.1.111.7a FEC degraded SER (1.201.4)                                                                                                                                                                                                                                |    |

|                                                                                                                                                                                                                                                                         |    |

| 45.2.1.111.7b FEC degraded SER ability (1.201.3)                                                                                                                                                                                                                        |    |

| 45.2.1.111.8 RS-FEC high SER (1.201.2)                                                                                                                                                                                                                                  |    |

| 45.2.1.111.9 FEC bypass indication ability (1.201.1)                                                                                                                                                                                                                    |    |

| 45.2.1.117 RS-FEC BIP error counter lane 0 (Register 1.230)                                                                                                                                                                                                             | 55 |

| 45.2.1.129 50GAUI-n, 100GAUI-2, 200GAUI-n, and 400GAUI-n chip-to-chip transmitter                                                                                                                                                                                       |    |

| equalization, receive direction, lane 0 register (Register 1.500)                                                                                                                                                                                                       |    |

| 45.2.1.129.1 Request flag (1.500.15)                                                                                                                                                                                                                                    |    |

| 45.2.1.129.2 Post-cursor request (1.500.14:12)                                                                                                                                                                                                                          |    |

| 45.2.1.129.3 Pre-cursor request (1.500.11:10)                                                                                                                                                                                                                           |    |

| 45.2.1129.4 Post-cursor remote setting (1.500.9:7)                                                                                                                                                                                                                      |    |

| 45.2.1.129.5 Pre-cursor remote setting (1.500.6:5)                                                                                                                                                                                                                      | 58 |

| 45.2.1.129.6 Post-cursor local setting (1.500.4:2)                                                                                                                                                                                                                      |    |

| 45.2.1.129.7 Pre-cursor local setting (1.500.1:0)                                                                                                                                                                                                                       | 58 |

| 45.2.1.130 50GAUI-n, 100GAUI-2, 200GAUI-n, and 400GAUI-n chip-to-chip transmitter                                                                                                                                                                                       |    |

| equalization, receive direction, lane 1 through lane 15 registers (Registers                                                                                                                                                                                            |    |

| 1.501 through 1.515)                                                                                                                                                                                                                                                    | 58 |

| 45.2.1.131 50GAUI-n, 100GAUI-2, 200GAUI-n, and 400GAUI-n chip-to-chip transmitter                                                                                                                                                                                       |    |

| equalization, transmit direction, lane 0 register (Register 1.516)                                                                                                                                                                                                      | 58 |

| 45.2.1.131.1 Request flag (1.516.15)                                                                                                                                                                                                                                    |    |

| 45.2.1.131.2 Post-cursor request (1.516.14:12)                                                                                                                                                                                                                          |    |

| 45.2.1.131.2 Post-cursor request (1.516.11:10)                                                                                                                                                                                                                          |    |

|                                                                                                                                                                                                                                                                         |    |

| 45.2.1.131.4 Post-cursor remote setting (1.516.9:7)                                                                                                                                                                                                                     |    |

| 45.2.1.131.5 Pre-cursor remote setting (1.516.6:5)                                                                                                                                                                                                                      |    |

| 45.2.1.131.6 Post-cursor local setting (1.516.4:2)                                                                                                                                                                                                                      |    |

| 45.2.1.121.7 Pro ourser level setting (1.516.1:0)                                                                                                                                                                                                                       | 61 |

|     | 45.2.1.132 50GAUI-n, 100GAUI-2, 200GAUI-n, and 400GAUI-n chip-to-chip transmitter     |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | equalization, transmit direction, lane 1 through lane 15 registers (Registers         |    |

|     | 1.517 through 1.531)                                                                  | 61 |

|     | 45.2.1.132a PMA precoder control Tx output (Register 1.600)                           | 61 |

|     | 45.2.1.132a.1 Lane 3 Tx output precoder enable (1.600.3)                              |    |

|     | 45.2.1.132a.2 Lane 2 Tx output precoder enable (1.600.2)                              |    |

|     | 45.2.1.132a.3 Lane 1 Tx output precoder enable (1.600.1)                              |    |

|     | 45.2.1.132a.4 Lane 0 Tx output precoder enable (1.600.0)                              |    |

|     | 45.2.1.132b PMA precoder control Rx input (Register 1.601)                            |    |

|     | 45.2.1.132b.1 Lane 3 Rx input precoder enable (1.601.3)                               |    |

|     | 45.2.1.132b.2 Lane 2 Rx input precoder enable (1.601.2)                               |    |

|     | 45.2.1.132b.3 Lane 1 Ry input precoder enable (1.601.1)                               | 62 |

|     | 45.2.1.132b.3 Lane 1 Rx input precoder enable (1.601.1)                               | 62 |

|     | 45.2.1.1320 PMA proceeder control Py output (Pegister 1 602)                          | 62 |

|     | 45.2.1.132c PMA precoder control Rx output (Register 1.602)                           | 03 |

|     | 45.2.1.132c.1 Lane 1 KX output precoder enable (1.602.1)                              | 03 |

|     | 45.2.1.132c.2 Lane 0 Rx output precoder enable (1.602.0)                              | 63 |

|     | 45.2.1.132d PMA precoder control 1x input (Register 1.603)                            | 63 |

|     | 45.2.1.132d.1 Lane 1 1x input precoder enable (1.603.1)                               | 63 |

|     | 45.2.1.132d.2 Lane 0 Tx input precoder enable (1.603.0)                               | 63 |

|     | 45.2.1.132d PMA precoder control Tx input (Register 1.603)                            | 64 |

|     | 45.2.1.132e.1 Tx input precoder request flag (1.604.1)                                | 64 |

|     | 45.2.1.132e.1 Tx input precoder request flag (1.604.1)                                | 64 |

|     | 45.2.1.132f PMA precoder request Rx input status (Register 1.605)                     | 64 |

|     | 45.2.1.132f.1 Lane 1 Rx input precoder request status (1.605.1)                       |    |

|     | 45.2.1.132f.2 Lane 0 Rx input precoder request status (1.605.0)                       | 64 |

|     | 45.2.1.132g PMA precoder request Tx input status (Register 1.606)                     | 65 |

|     | 45.2.1.132g.1 Lane 1 Tx input precoder request status(1.606.1)                        |    |

|     | 45.2.1.132g.2 Lane 0 Tx input precoder request status (1.606.0)                       | 65 |

|     | 45.2.1.132h RS-FEC degraded SER activate threshold register (Register 1.650, 1.651)   |    |

|     | 45.2.1.132i RS-FEC degraded SER deactivate threshold register (Register 1.652, 1.653) |    |

|     | 45.2.1.132j RS-FEC degraded SER interval register (Register 1.654, 1.655)             |    |

|     | 45.2.1.135a BASE-R PAM4 PMD training LP control, lane 0 through lane 3 registers      |    |

|     | (Register 1.1120 through 1.1123)                                                      | 67 |

|     | 45.2.1.136a BASE-R PAM4 PMD training LP status, lane 0 through lane 3 registers       |    |

|     | (Register C1220 through 1.1223)                                                       | 68 |

|     | 45.2.1.137a BASE-R PAM4 PMD training LD control, lane 0 through lane 3 registers      | 00 |

|     | (Register 1.1320 through 1.1323)                                                      | 69 |

|     | 45.2.1.138a BASE-R PAM4 PMD training LD status, lane 0 through lane 3 registers       | 07 |

|     | Register 1.1420 through 1.1423)                                                       | 70 |

|     | 45.2.1.139 PMD training pattern lanes 0 through 3 (Register 1.1450 through 1.1453)    |    |

|     | 45.2.1.141 PRBS pattern testing control (Register 1.1501)                             |    |

| 15  |                                                                                       |    |

| 43  | 2.3 PCS registers                                                                     |    |

| "   | 45.2.3.1 PCS control 1 register (Register 3.0)                                        |    |

| Sh. | 45.2.3.2 PCS status 1 register (Register 3.1)                                         |    |

| 1   | 45.2.3.2.7 PCS receive link status (3.1.2)                                            |    |

|     | 45.2.3.4 PCS speed ability (Register 3.4)                                             |    |

|     | 45.2.3.4.5a 50G capable (3.4.5)                                                       |    |

|     | 45.2.3.6 PCS control 2 register (Register 3.7)                                        |    |

|     | 45.2.3.7 PCS status 2 register (Register 3.8)                                         |    |

|     | 45.2.3.7.6a 50GBASE-R capable (3.8.8)                                                 |    |

|     | 45.2.3.10 EEE control and capability 1 (Register 3.20)                                |    |

|     | 45.2.3.10.a 50GBASE-R EEE fast wake supported (3.20.14)                               |    |

|     | 45.2.3.15 BASE-R and MultiGBASE-T PCS status 1 register (Register 3.32)               | 75 |

|     | 45.2.3.15.1 BASE-R and MultiGBASE-T receive link status (3.32.12)                     | 75 |

| 45.2.3.15.4 BASE-R and MultiGBASE-T PCS high BER (3.32.1)                                 | 75       |

|-------------------------------------------------------------------------------------------|----------|

| 45.2.3.15.5 BASE-R and MultiGBASE-T PCS block lock (3.32.0)                               | 75       |

| 45.2.3.16 BASE-R and MultiGBASE-T PCS status 2 register (Register 3.33)                   | 75       |

| 45.2.3.16.1 Latched block lock (3.33.15)                                                  | 75       |

| 45.2.3.16.2 Latched high BER (3.33.14)                                                    | 75       |

| 45.2.3.16.3 BER (3.33.13:8)                                                               |          |

| 45.2.3.16.4 Errored blocks (3.33.7:0)                                                     |          |

| 45.2.3.19 BASE-R PCS test-pattern control register (Register 3.42)                        |          |

| 45.2.7 Auto-Negotiation registers                                                         |          |

| 45.2.7.12 Backplane Ethernet, BASE-R copper status (Register 7.48)                        |          |

| 45.2.7.12.3 Negotiated Port Type (7.48.1, 7.48.2, 7.48.3, 7.48.5, 7.48.6, 7.48.8, 7.48.9, | 20       |

| 7.48.10, 7.48.11, 7.48.12, 7.48.13, 7.48.14, 7.48.15, 7.49.0, 7.49.1, 7.49.2)             | 7.       |

| 7.49.2)                                                                                   | 76       |

| 45.2.7.12a Backplane Ethernet, BASE-R copper status 2 (Register 7.49)                     | 77       |

| 45.2.7.12a.1 Negotiated Port Type                                                         | 77       |

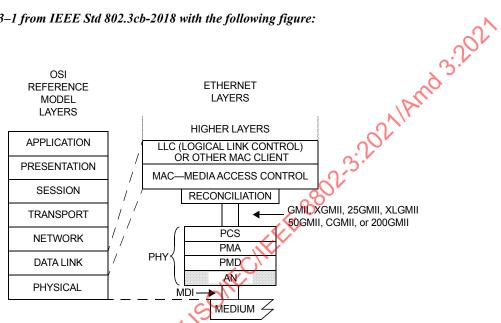

| 69. Introduction to Ethernet operation over electrical backplanes                         |          |

| 69. Introduction to Ethernet operation over electrical backplanes                         | 78       |

| 69.1 Overview                                                                             | 70       |

| 69.1 Overview                                                                             | 78       |

| 69.1.1 Scope                                                                              | /8       |

| 69.1.2 Relationship of Backplane Ethernet to the ISO OSI reference model                  |          |

| 69.2 Summary of Backplane Ethernet Sublayers                                              | 80       |

| 69.2.1 Reconciliation subjayer and media independent interfaces                           | 80       |

| 69.2.3 Physical Layer signaling systems 69.3 Delay constraints                            | 80<br>22 |

| 69.5 Protocol implementation conformance statement (PICS) proforma                        | 02<br>22 |

| 07.5 1 rotocol implementation comormance statement (Fres) proforma                        | 02       |

| 73. Auto-Negotiation for backplane and copper cable assembly                              | 83       |

|                                                                                           |          |

| 73.2 Relationship to the ISO/IEC Open Systems Interconnection (OSI) reference model       | 83       |

| 73.5 DME transmission                                                                     | 83       |

| 73.5.1 DME electrical specifications                                                      |          |

| 73.6 Link codeword encoding                                                               |          |

| 73.6.4 Technology Ability Field                                                           |          |

| 73.7 Receive function requirements                                                        |          |

| 73.7.6 Priority Resolution function                                                       |          |

| 73.10 State diagrams and variable definitions                                             |          |

| 73.10.1 State diagram variables                                                           |          |

| 73.10.2 State diagram timers                                                              | 87       |

| 78. Energy-Efficient Ethernet (EEE)                                                       | 00       |

| 78. Energy-Entrent Ethernet (BBE)                                                         | 00       |

| 78.1 Overview                                                                             | 88       |

| 78.1.4 PHY types optionally supporting EEE                                                |          |

| 78.5 Communication link access latency                                                    |          |

| 76.5 Communication mik access latency                                                     | 67       |

| 80. Introduction to 40 Gb/s and 100 Gb/s networks                                         | 90       |

|                                                                                           |          |

| 80.1 Overview                                                                             |          |

| 80.1.3 Relationship of 40 Gigabit and 100 Gigabit Ethernet to the ISO OSI reference model |          |

| 80.1.4 Nomenclature                                                                       |          |

| 80.1.5 Physical Layer signaling systems                                                   |          |

| 80.2 Summary of 40 Gigabit and 100 Gigabit Ethernet sublayers                             | 93<br>93 |

| AU Z Z PHVSICAL COMPG SUDIAVEL (PCS)                                                      | 94       |

|            | 80.2.3 Forward Error Correction (FEC) sublayers                                                                                                       | 93  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | 80.2.4 Physical Medium Attachment (PMA) sublayer                                                                                                      |     |

|            | 80.2.5 Physical Medium Dependent (PMD) sublayer                                                                                                       |     |

|            | 80.2.6 Auto-Negotiation                                                                                                                               |     |

|            | 80.4 Delay constraints                                                                                                                                |     |

|            | 80.5 Skew constraints                                                                                                                                 |     |

|            | 80.7 Protocol implementation conformance statement (PICS) proforma.                                                                                   |     |

|            | 50.7 Trotocol implementation comormance statement (1105) proforma                                                                                     | ))  |

| 82.        | . Physical Coding Sublayer (PCS) for 64B/66B, type 40GBASE-R and 100GBASE-R                                                                           | 100 |

|            | 82.6 Auto-Negotiation                                                                                                                                 | 001 |

|            | 82.7 Protocol implementation conformance statement (PICS) proforma for Clause 82. Physical                                                            |     |

|            | Coding Sublayer (PCS) for 64B/66B, type 40GBASE-R and 100GBASE-R                                                                                      | 100 |

|            | 82.7.4 PICS proforma tables for PCS, type 40GBASE-R and 100GBASE-R                                                                                    | 100 |

|            | 82.7.4 PICS proforma tables for PCS, type 40GBASE-R and 100GBASE-R 82.7.4.11 Auto-Negotiation for Backplane Ethernet functions                        | 100 |

|            | $\gamma$                                                                                                                                              |     |

| 90.        | . Ethernet support for time synchronization protocols                                                                                                 | 101 |

|            |                                                                                                                                                       |     |

|            | 90.1 Introduction                                                                                                                                     | 101 |

|            | Ethernet support for time synchronization protocols.  90.1 Introduction.  Reed-Solomon Forward Error Correction (RS-FEC) sublayer for 100GRASE-R PHVs |     |

| 91.        | . Reed-Solomon Forward Error Correction (RS-FEC) sublayer for 100GBASE-R PHYs                                                                         | 102 |

|            |                                                                                                                                                       |     |

|            | 91.3 PMA compatibility                                                                                                                                | 102 |

|            | 91.3 PMA compatibility 91.5 Functions within the RS-FEC sublayer 91.5.2 Transmit function                                                             | 102 |

|            | 91.5.2 Transmit function                                                                                                                              | 102 |

|            | 91.5.2.6 Alignment marker mapping and insertion.                                                                                                      | 102 |

|            | 91.5.2.7 Reed-Solomon encoder                                                                                                                         | 102 |

|            | 91.5.2.7 Reed-Solomon encoder 91.5.3 Receive function                                                                                                 | 103 |

|            | 91.5.3.3 Reed-Solomon decoder                                                                                                                         | 103 |

|            | 91.5.3.3.1 FEC Degraded SER (optional)                                                                                                                |     |

|            | 91.6 RS-FEC MDIO function mapping                                                                                                                     | 104 |

|            | 91.6.2a four_lane_pmd                                                                                                                                 |     |

|            | 91.6.2b FEC degraded SER enable                                                                                                                       |     |

|            | 91.6.2c FEC_degraded_SER_activate_threshold                                                                                                           |     |

|            | 91.6.2d FEC_degraded_SER_deactivate_threshold                                                                                                         |     |

|            | 91.6.2e FEC degraded SER interval                                                                                                                     |     |

|            | 91.6.5a FEC degraded SER ability                                                                                                                      |     |

|            | 91.6.5b FEC_degraded_SER                                                                                                                              |     |

|            | 91.7 Protocol implementation conformance statement (PICS) proforma for Clause 91, Reed-                                                               | 103 |

|            | Solomon Forward Error Correction (RS-FEC) sublayer for 100GBASE-R PHYs                                                                                | 105 |

|            | 91.7.3 Major capabilities/options                                                                                                                     |     |

|            | 91.7.4 PICS proforma tables for Reed-Solomon Forward Error Correction (RS-FEC) sublayer                                                               | 103 |

|            | for 100GBASE-R PHYs                                                                                                                                   | 106 |

|            |                                                                                                                                                       |     |

|            | 91.7.4.1 Transmit function                                                                                                                            |     |

| $\nearrow$ | 91.7.4.2 Receive function                                                                                                                             | 100 |

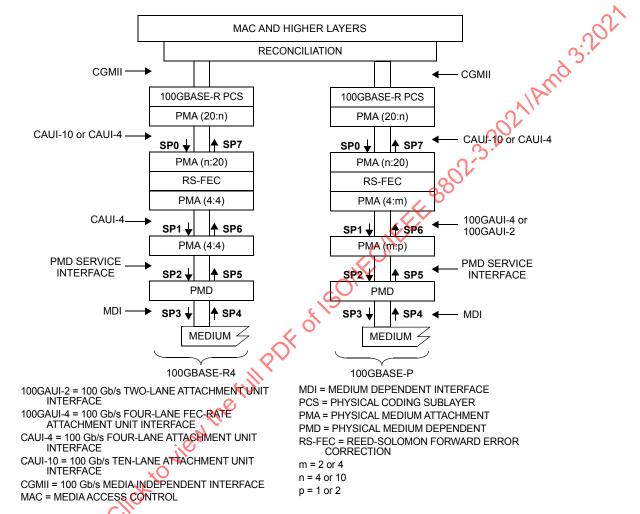

| 11         | 6. Introduction to 200 Gb/s and 400 Gb/s networks                                                                                                     | 100 |

| 110        | 0. Illifoduction to 200 Gb/s and 400 Gb/s networks                                                                                                    | 108 |

|            | 116.1 Overview                                                                                                                                        | 108 |

|            | 116.1.2 Relationship of 200 Gigabit and 400 Gigabit Ethernet to the ISO OSI reference                                                                 | 100 |

|            |                                                                                                                                                       | 100 |

|            | model                                                                                                                                                 |     |

|            | 116.1.3 Nomenclature                                                                                                                                  |     |

|            | 116.1.4 Physical Layer signaling systems                                                                                                              |     |

|            | 116.2 Summary of 200 Gigabit and 400 Gigabit Ethernet sublayers                                                                                       | 110 |

| 116.2.5 Physical Medium Dependent (PMD) sublayer                                                                                                | 110        |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 116.4 Delay constraints                                                                                                                         |            |

| 119. Physical Coding Sublayer (PCS) for 64B/66B, type 200GBASE-R and 400GBASE-R                                                                 | 111        |

| 177.1 11/5.001. County 5. (1 Co) 101 0 12/002, 0/pt 200 02/102 10 and 100 02/102 10 minimum.                                                    |            |

| 119.5a Auto-Negotiation                                                                                                                         | 111        |

| 119.6 Protocol implementation conformance statement (PICS) proforma for Clause 119, Physical                                                    |            |

| Coding Sublayer (PCS) for 64B/66B, type 200GBASE-R and 400GBASE-R                                                                               | 111        |

| 119.6.4 PICS proforma tables for Physical Coding Sublayer (PCS) 64B/66B, type                                                                   |            |

| 200GBASE-R and 400GBASE-R                                                                                                                       | 111        |

| 119.6.4.12 Auto-Negotiation for Backplane Ethernet functions                                                                                    | <b>O</b> 1 |

| 120. Physical Medium Attachment (PMA) sublayer, type 200GBASE-R and 400GBASE-R                                                                  | 112        |

| 120.5 Functions within the PMA                                                                                                                  | 112        |

|                                                                                                                                                 |            |

| 120.5.7 1 Gray manning for PAMA encoded lanes                                                                                                   | 112        |

| 120.5.7.1 Gray mapping for PAMA encoded lanes                                                                                                   | 112        |

| 120.5.7.1 Gray mapping for PAM4 encoded lanes                                                                                                   | 112        |

| 120.7 Protocol implementation conformance statement (PICS) proforma for Clause 120, Physical                                                    | 112        |

| Medium Attachment (PMA) sublayer, type 200GBASE-R and 400GBASE-R                                                                                | 113        |

|                                                                                                                                                 |            |

| 120.7.7 Encoding                                                                                                                                | 113        |

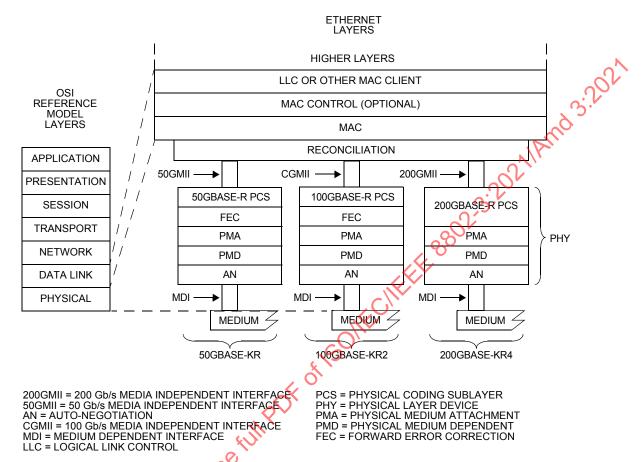

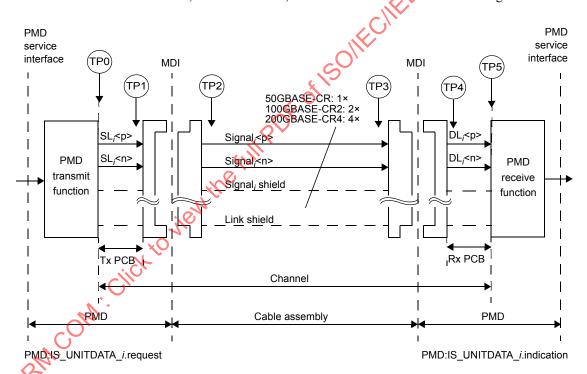

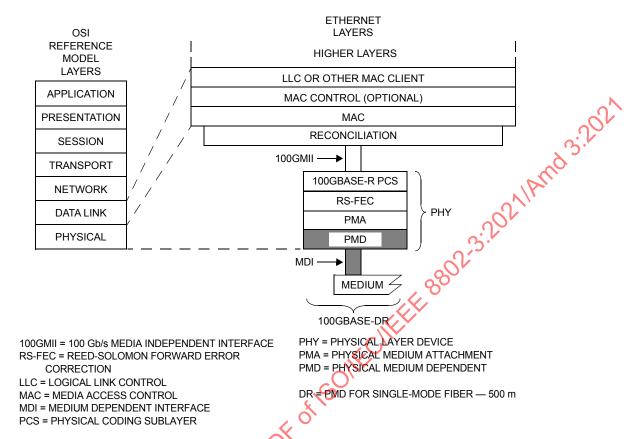

| 131. Introduction to 50 Gb/s networks  131.1 Overview  131.1.1 Scope  131.1.2 Relationship of 50 Giochit Ethomat & the ISO OSI of Farmers model | 114        |

| ~O/\*.                                                                                                                                          |            |

| 131.1 Overview                                                                                                                                  | 114        |

| 131.1.1 Scope                                                                                                                                   | 114        |

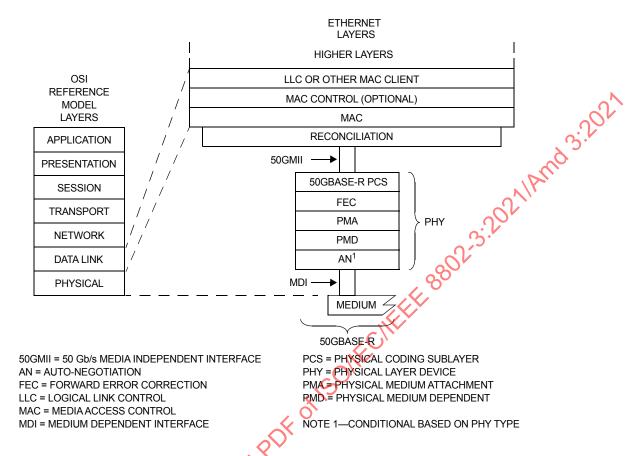

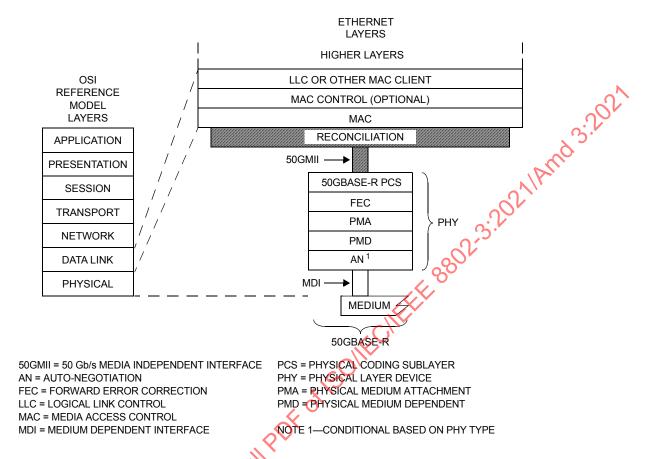

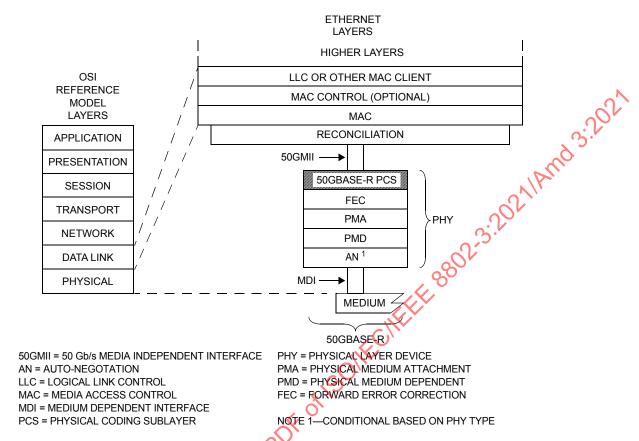

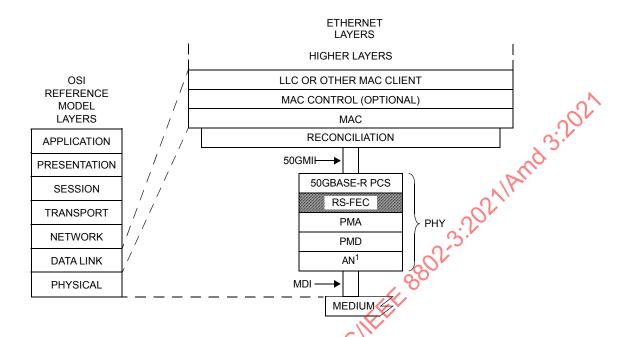

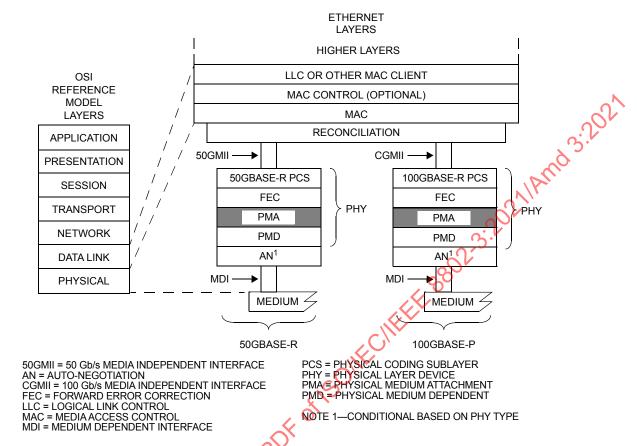

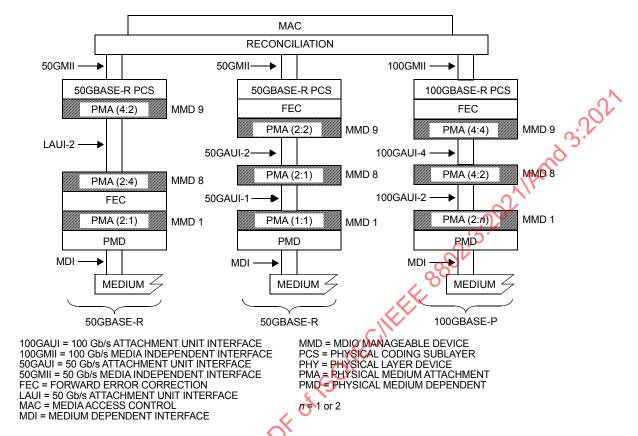

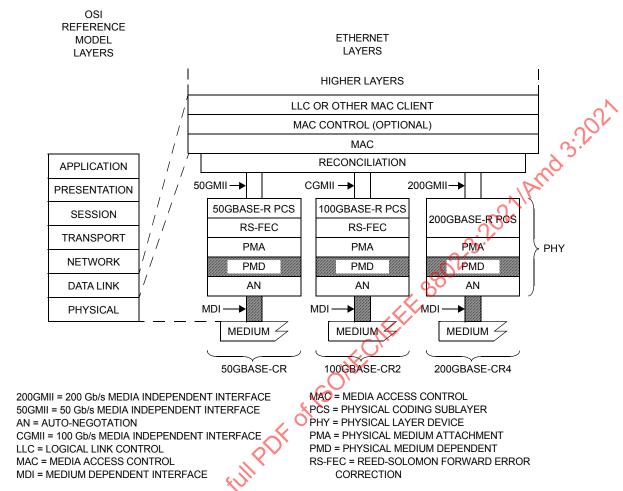

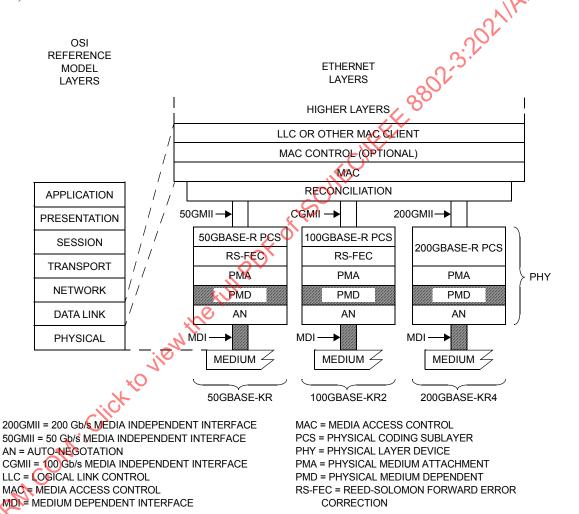

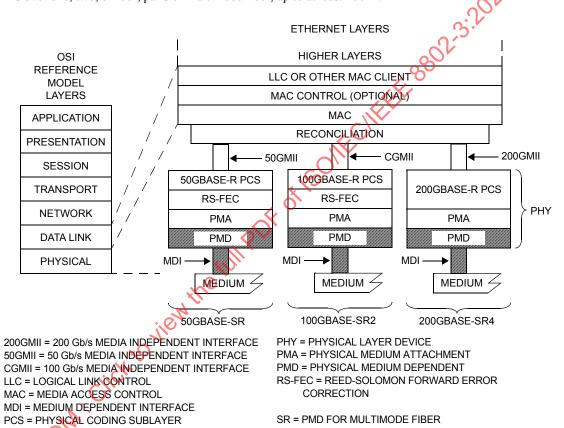

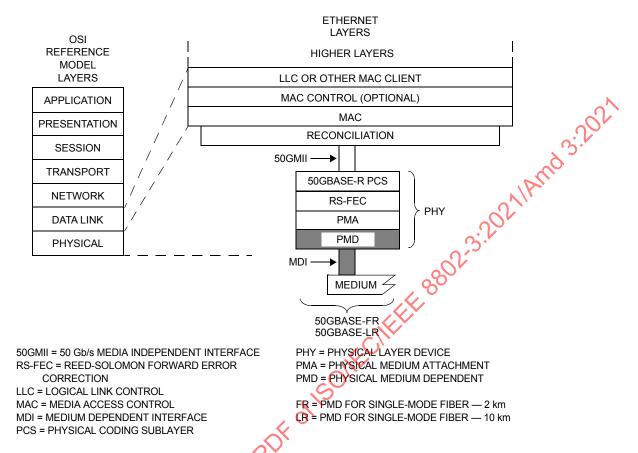

| 131.1.2 Relationship of 50 Gigabit Ethernet to the ISO OSI reference model                                                                      | 114        |

| 131.1.3 Nomenclature                                                                                                                            | 114        |

| 131.1.4 Physical Layer signaling systems                                                                                                        | 116        |

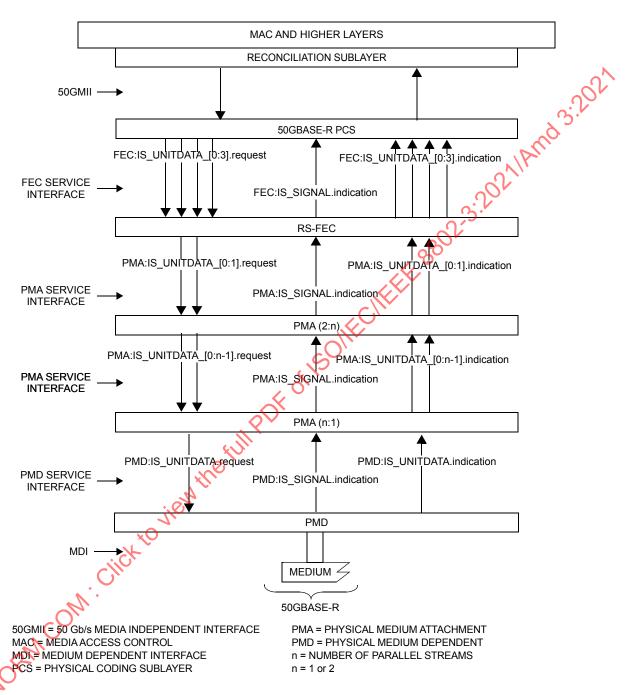

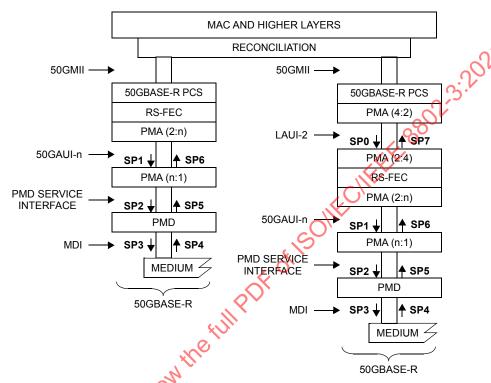

| 131.2 Summary of 50 Gigabit Ethernet sublayers                                                                                                  |            |

| 131.2.1 Reconciliation Sublayer (RS) and Media Independent Interface (50GMII)                                                                   | 117        |

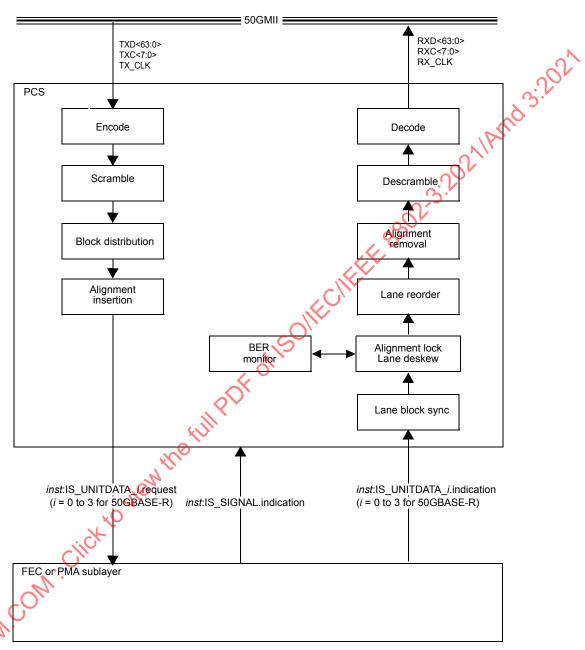

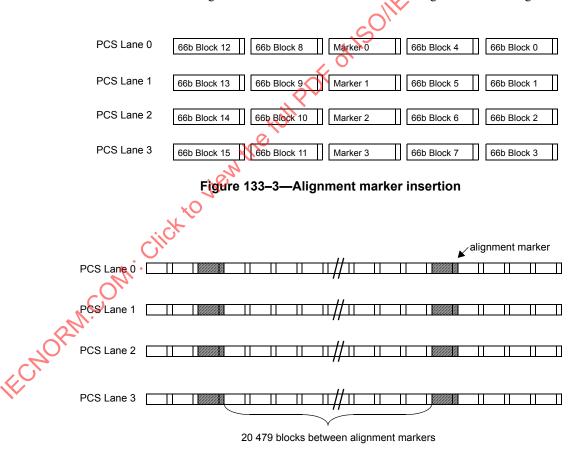

| 131.2.2 Physical Coding Sublayer (PCS)                                                                                                          |            |

| 131.2.3 Forward Error Correction (FEC) sublayer                                                                                                 |            |

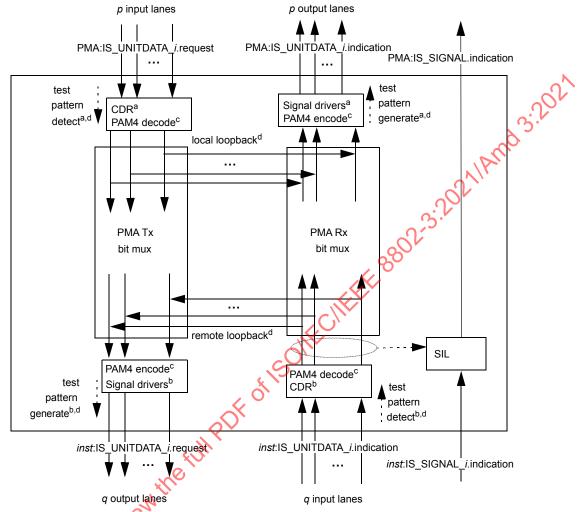

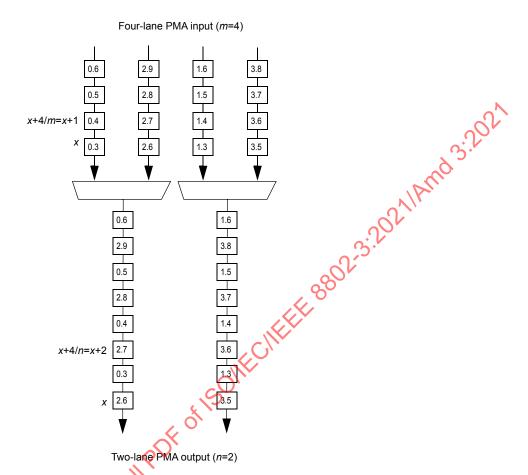

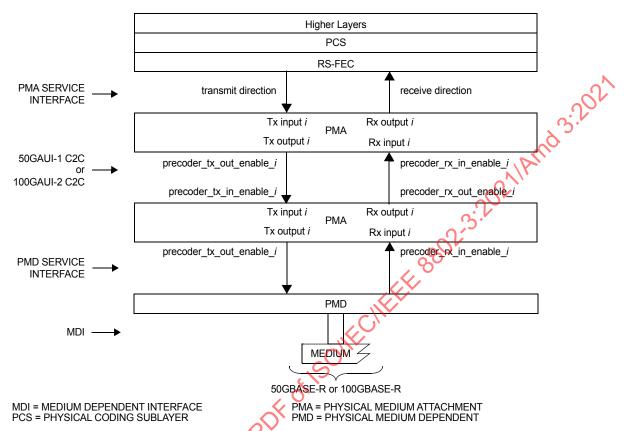

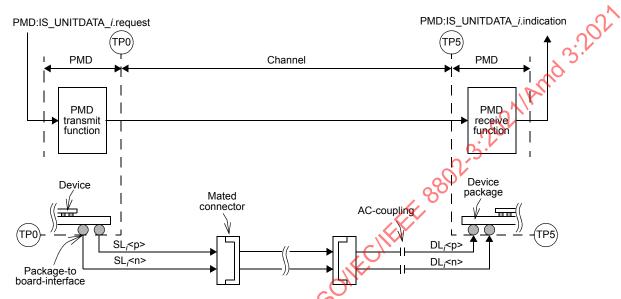

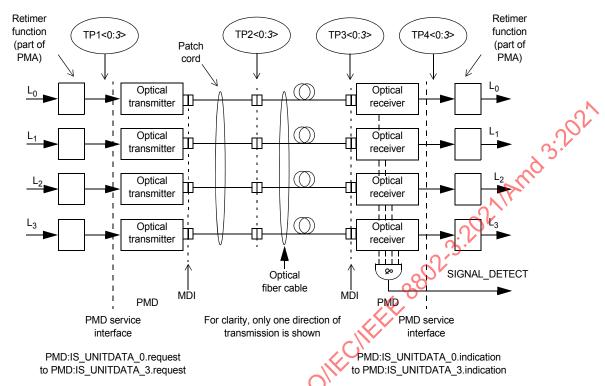

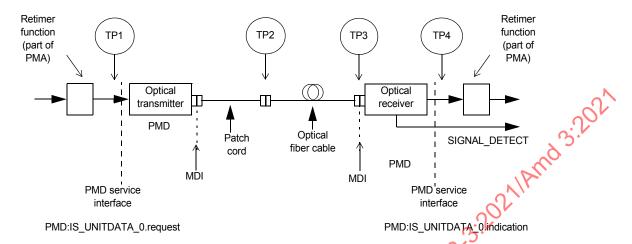

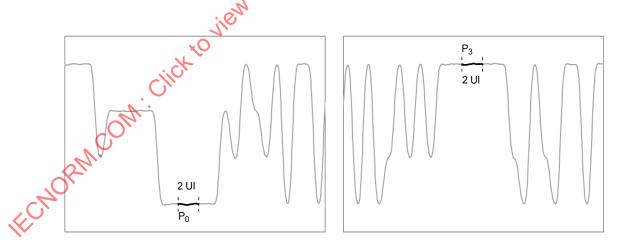

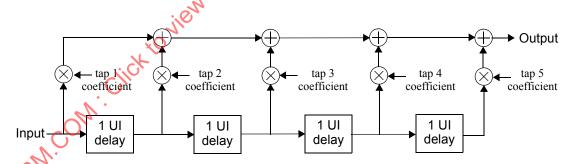

| 131.2.4 Physical Medium Attachment (PMA) sublayer                                                                                               |            |

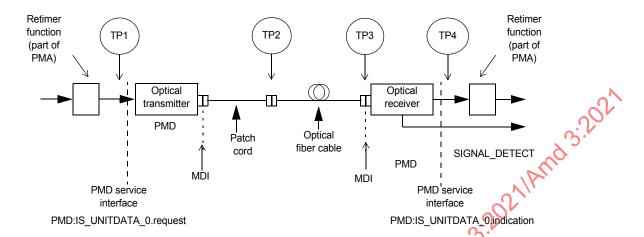

| 131.2.5 Physical Medium Dependent (PMD) sublayer                                                                                                |            |