# **INTERNATIONAL STANDARD**

# ISO/IEC 26908

Second edition 2009-11-15

Information technology -Telecommunications and information exchange between systems — MAC-PHY interface for ISO/IEC 26907

Technologies de l'information — Téléinformatique — Interface MAC-PHY pour l'ISO/CEI 26907

AY pour AY pour lich to viennthe full Pills

#### PDF disclaimer

This PDF file may contain embedded typefaces. In accordance with Adobe's licensing policy, this file may be printed or viewed but shall not be edited unless the typefaces which are embedded are licensed to and installed on the computer performing the editing. In downloading this file, parties accept therein the responsibility of not infringing Adobe's licensing policy. The ISO Central Secretariat accepts no liability in this area.

Adobe is a trademark of Adobe Systems Incorporated.

Details of the software products used to create this PDF file can be found in the General Info relative to the file; the PDF-creation parameters were optimized for printing. Every care has been taken to ensure that the file is suitable for use by ISO member bodies. In the unlikely event that a problem relating to it is found, please inform the Central Secretariat at the address given below.

# **COPYRIGHT PROTECTED DOCUMENT**

#### © ISO/IEC 2009

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Published in Switzerland

# **Contents**

Page

| Forewo       | ord                                                       | v                    |

|--------------|-----------------------------------------------------------|----------------------|

| Introdu      | uction                                                    | vi                   |

| 1            | Scope                                                     | 1                    |

| 2            | Conformance                                               | 1                    |

| _            | Normative references                                      |                      |

| 3            | Normative references                                      | 1                    |

| 4            | Terms and definitions                                     | 1                    |

| 5            | Notational conventions                                    | 1                    |

| 6            | Abbreviations and acronyms                                | 2                    |

| 7            | Overview                                                  | 2                    |

| 8            | Interface Signal Description                              | 3                    |

| 8.1          | Interface Signal Descriptions                             | 4                    |

| 8.1.1        | Control Interface                                         | 4                    |

| 8.1.2        | Data Interface                                            | 5                    |

| 8.1.3        | CCA Interface                                             | 5                    |

| 8.1.4        | Management Interface                                      | 5                    |

| 8.2          | PHY Operational State                                     | 6                    |

| •            | Paristone W.                                              | ^                    |

| 9<br>9.1     | Registers                                                 | b                    |

| 9.1<br>9.2   | Register Address Spaces                                   | b                    |

| 9.2          | Static Parameter Definitions                              |                      |

| 9.3          | Static Parameter Coding                                   |                      |

| 9.4<br>9.5   | Dynamic Register Definitions Q                            | 1 1<br>1 <i>1</i>    |

| 9.6          | Register Map                                              | 1 <del>4</del><br>16 |

| 9.7          | Register Set Access Timing                                |                      |

| 9.7.1        | Transmit Control Registers                                |                      |

| 9.7.2        | Receive Control Registers                                 |                      |

| 9.8          | TONE-NULLING MAP CONTROL                                  |                      |

|              |                                                           |                      |

| 10           | Frame Structures                                          |                      |

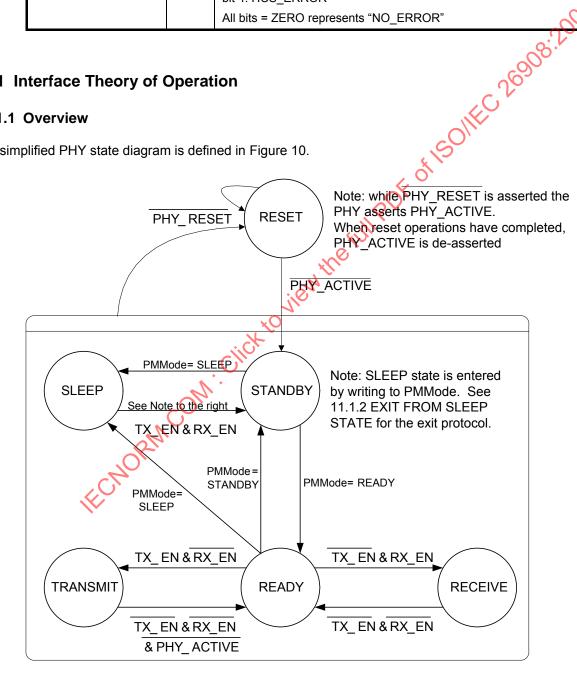

| 11           | Interface Theory of Operation                             | 24                   |

| 11.1         | Overview                                                  |                      |

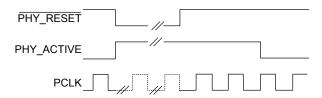

| 11.1.1       | PHY Reset Protocol                                        |                      |

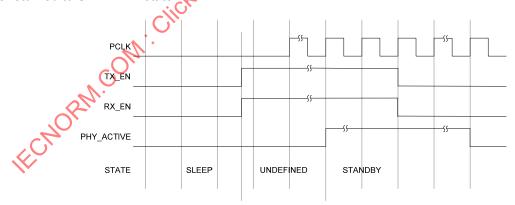

| 11.1.2       |                                                           |                      |

|              | Normal Operation                                          |                      |

| 11.2         | Frame Timing                                              |                      |

| 11.3         | Ranging Support                                           |                      |

| 11.4<br>11.5 | Transceiver Delay DefinitionsTransceiver Turnaround Times |                      |

| 11.5.1       | RX-TX Turnaround Time                                     | _                    |

| 11.5.1       |                                                           |                      |

| 11.5.2       | PREAMBLE CONTROL                                          |                      |

| 11.6.1       | Single Frame Transmission and Reception                   |                      |

| 11.6.2       |                                                           |                      |

| 11.6.2       |                                                           |                      |

| 11.7         | Transmit Operation                                        |                      |

| 11.7.1       | Data Bus Ownership                                        |                      |

|              | Single Frame Transmission Control                         |                      |

# ISO/IEC 26908:2009(E)

| 11.7.3                   | Burst Mode Transmission Control                   | 33             |

|--------------------------|---------------------------------------------------|----------------|

| 11.7.4                   | Burst Mode Transmit Error Recovery                | 34             |

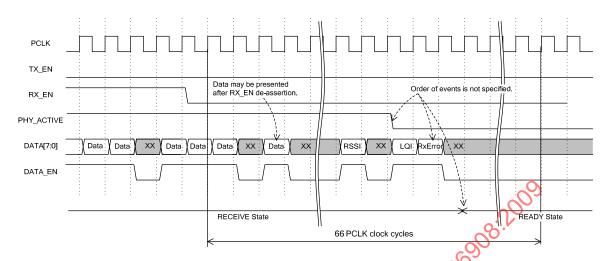

| 11.8                     | Receive Operation                                 |                |

| 11.8.1                   | Data Bus Ownership                                |                |

|                          | Single Frame Reception Control                    |                |

|                          | Burst Mode Reception Control                      |                |

|                          | Burst Mode Reception Error Recovery               |                |

| _                        | Zero Length Frame Reception                       |                |

| 11.9                     | MAC Transmit Abort                                |                |

|                          | MAC Receive Abort                                 |                |

| 11.11                    | Error Conditions                                  |                |

|                          | Transmit Error Conditions                         |                |

|                          | Receive Error Conditions                          |                |

| 11.11. <u>~</u><br>11.12 | Clear Channel Assessment                          | 41             |

| 11.12<br>11.12.1         | CCA Interface Signals                             | 42             |

| 11.12.1<br>11 12 2       | Operation of the CCA Interface                    | <del></del> 72 |

| 11.12.2<br>11 12         | Management Interface                              | <del>4</del> 2 |

| 11.13<br>11 12 1         | Management Interface Signals                      | 43             |

| 11.13.1<br>44 42 2       | Management Interface Signals                      | 43             |

| 11.13.Z<br>11 12 2       | Examples                                          | 43             |

| 11.13.3                  | Examples                                          | 45             |

| Annex                    | A (informative) Electrical Specifications         | 47             |

| A.1                      | I/O DC Requirements                               | 47             |

| A.1.1                    | 3,3V DC Specification                             | 47             |

| A.1.2                    | 1,8V DC Specification                             |                |

| A.1.3                    | 1.2V DC Specification                             | 47             |

| A.2                      | MAC and PHY Timing Specifications                 | 48             |

| A.2.1                    | PHY Signal Timing                                 | 48             |

| A.2.2                    | PHY Signal TimingMAC Signal Timing                | 49             |

|                          |                                                   |                |

| Annex                    | B (informative) PHY Vendor and Version Coding     | 50             |

| B.1                      | PHYID Format and Coding                           | 50             |

| B.2                      | PHY Version Format and Coding                     | 50             |

|                          | B (informative) PHY Vendor and Version Coding (2) |                |

|                          |                                                   |                |

#### **Foreword**

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work. In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC 1.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part 2.

The main task of the joint technical committee is to prepare International Standards. Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting. Publication as an International Standard requires approval by at least 75 % of the national bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights.

ISO/IEC 26908 was prepared by Ecma International (as ECMA-369) and was adopted, under a special "fast-track procedure", by Joint Technical Committee ISO/IEC JTC 1, *Information technology*, in parallel with its approval by national bodies of ISO and IEC.

This second edition cancels and replaces the first edition (ISO/IEC 26908:2007), which has been technically revised.

# Introduction

ISO/IEC 26907 specifies the PHY and MAC for a high rate ultra wideband wireless transceiver. Implementations of ISO/IEC 26907 may expose the interface between the PHY and MAC as specified herein.

ECHORN.COM. Click to view the full Path of Echo Ren. Chick to view the full Path of Echo Ren. Chick to view the full Path of Echo Ren. Chick to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Path of Echo Ren. Com. Click to view the full Pa

# Information technology — Telecommunications and information exchange between systems — MAC-PHY interface for ISO/IEC 26907

# 1 Scope

This International Standard specifies the interface between implementations of the PHY and MAC as specified in ISO/IEC 26907.

#### 2 Conformance

PHY and MAC implementations of ISO/IEC 26907 conform to this International Standard by implementing the interface specified herein.

#### 3 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

ISO/IEC 26907:2009, Information technology — Telecommunications and information exchange between systems — High-rate ultra-wideband PHY and MAC standard (also published by Ecma as Standard ECMA-368)

#### 4 Terms and definitions

For the purposes of this document, the terms and definitions given in ISO/IEC 26907 apply.

# 5 Notational conventions

The use of the word *shall* is meant to indicate a requirement which is mandated by the Standard, i.e. it is required to implement that particular feature with no deviation in order to conform to the Standard. The use of the word *should* is meant to recommend one particular course of action over several other possibilities, however without mentioning or excluding these others. The use of the word *may* is meant to indicate that a particular course of action is permitted. The use of the word *can* is synonymous with is able to – it is meant to indicate a capability or a possibility.

All floating-point values have been rounded to 4 decimal places.

An exclamation mark preceding a signal indicates that the signal is active low.

#### Abbreviations and acronyms 6

BM **Burst Mode**

CCA Clear Channel Assessment

**CRC** Cyclic Redundancy Code

**FCS** Frame Check Sequence

FFI Fixed-Frequency Interleaving

HCS

LQI

Isb

MAC

**MIFS**

msb

PHY

Al Layer Convergence Protocol

Preamble Type

Received Signal Strength Indicators

Receive or Receiver

Thort Interframe Space

The Frequency

The Frequency **PLCP**

PT

**RSSI**

RX

**SIFS**

TF

**TFC** Time-Frequency Code

TFI Time-Frequency Interleaving

TX Transmit or Transmitter

#### 7 Overview

<u>Clause 8</u> defines the interface signals, their directions and functions.

Clause 9 defines the interface parameters and registers. A recommended mapping for PHY parameters is provided along with the register map for PHY registers and setup and hold timing for register access.

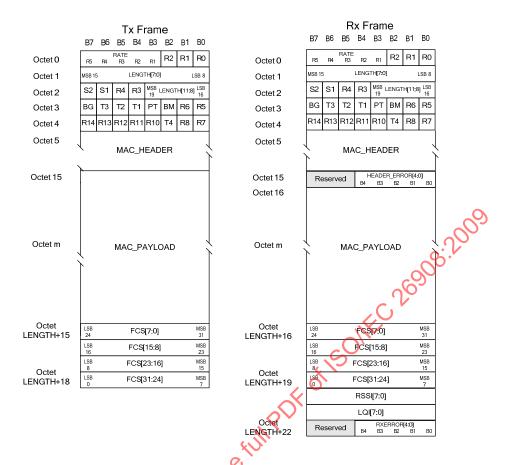

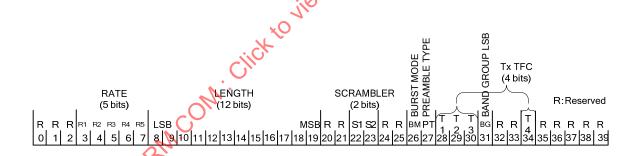

Clause 10 defines the frame formats for data exchanges over the interface.

Clause 11 is the Theory of Operation for the complete interface covering the PHY states and transitions, reset and sleep protocols, frame timing references, preamble control and transmit and receive operations for both single frame and burst mode operation as well as receive error cases. The section is completed by definition of the CCA and Management interface protocols.

There are two annexes to this specification. Annex A provides an Electrical Interface and Annex B defines formats for two managed identifiers.

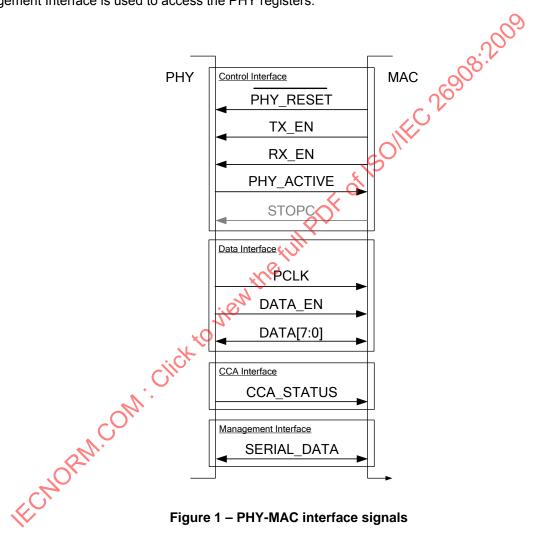

# 8 Interface Signal Description

The MAC-PHY signal interface is depicted in Figure 1. It consists of the Data Interface including an 8-bit data bus, the Control Interface, the CCA Interface and the Management Interface. The Data Interface, which is used to transfer data to and from the MAC, operates differently depending on the state of the PHY. The Control Interface is used by the MAC to control the operating state of the PHY and by the PHY to indicate TX/RX status to the MAC. The CCA Interface is used for Clear Channel Assessment status indication. The Management Interface is used to access the PHY registers.

Table 1, Table 2, Table 3 and Table 4 define the signals in the Control Interface, Data Interface, CCA Interface and Management Interface, respectively. The operational mode of the Data Interface in each PHY state is summarized in Table 5.

# 8.1 Interface Signal Definitions

# 8.1.1 Control Interface

Table 1 – Control Interface Signals

| SIGNAL           | Width<br>(Bits) | DIR        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| !PHY_RESET       | 1               | MAC to PHY | !PHY_RESET is asserted for PHY specific interval PHYResetTime to clear all PHY variables and reset the PHY to its initial state. The PHY writes STANDBY to PMMODE and transitions to STANDBY state after !PHY_RESET is de-asserted and reset operations have completed. !PHY_RESET is asynchronous to PCLK. !PHY_RESET is ACTIVE LOW.                                                                                                                                                                                                                                                                                                                                                                                                          |

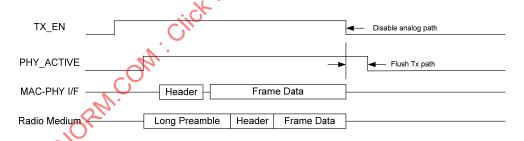

| TX_EN            | 1               | MAC to PHY | TX_EN is used to place the PHY in TRANSMIT State: [Its secondary use (with RX_EN) is to transition from SLEEP to STANDBY when the PHY clock source has been stopped for power saving.]  TX_EN is synchronous to PCLK except in SLEEP state.  TX_EN is ACTIVE HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RX_EN            | 1               | MAC to PHY | RX_EN is used to place the PHY in RECEIVE State. [Its secondary use (with TX_EN) is to transition from SLEEP to STANDBY when the PHY clock source has been stopped for power saving.]  RX_EN is synchronous to PCLK except in SLEEP state.  RX_EN is ACTIVE HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

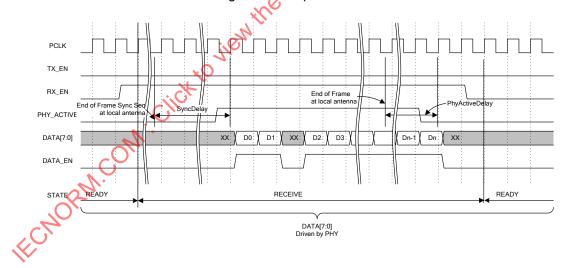

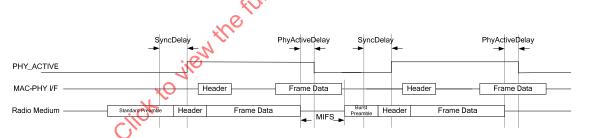

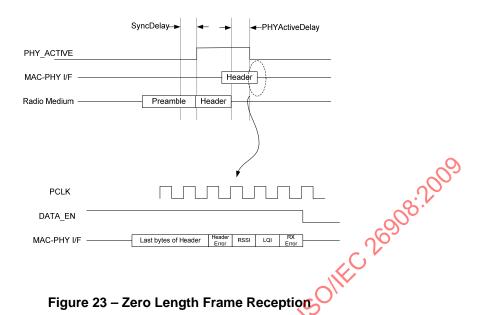

| PHY_ACTIVE       | 1               | PHY to MAC | PHY_ACTIVE is used by the PHY to indicate that it is either transmitting or receiving a frame over the air. In TRANSMIT state, the rising edge of PHY_ACTIVE indicates the start of frame at the local antenna and the falling edge indicates that the entire frame has been transmitted over the air. In RECEIVE state, the rising edge of this signal indicates that the start of the preamble has been detected (SyncDelay + the preceding synchronization fields earlier) and the falling edge indicates that the entire frame has been received (PHYActiveDelay earlier) at the local antenna. PHY_ACTIVE is also used in the special cases of Exit from SLEEP and RESET.  PHY_ACTIVE is synchronous to PCLK.  PHY_ACTIVE is ACTIVE HIGH. |

| STOPC (optional) | CHI             | MAC to PHY | On/Off signal for PCLK in STANDBY state. PCLK is active when STOPC is de-asserted and not active when STOPC is asserted.  STOPC is asynchronous to PCLK.  STOPC is ACTIVE HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 8.1.2 Data Interface

Table 2 - Data Interface Signals

| SIGNAL    | Width<br>(Bits) | DIR            | DESCRIPTION                                                                                                                                                                                                                                       |

|-----------|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

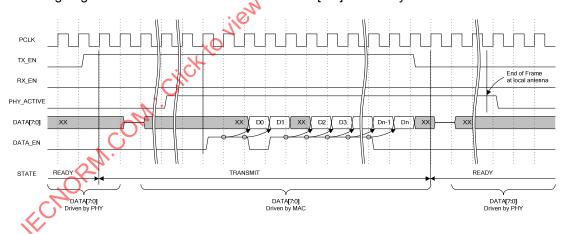

| PCLK      | 1               | PHY to MAC     | Interface clock provided by the PHY. Interface signals are synchronous to the rising edge of PCLK (see Annex A).  The nominal rate of PCLK is 66MHz.                                                                                              |

| DATA_EN   | 1               | PHY to MAC     | In TRANSMIT state, this signal is used by the PHY to request more data from the MAC. In RECEIVE state, it is used to indicate to the MAC that there is valid data on the DATA[7:0] bus.  DATA_EN is synchronous to PCLK.  DATA_EN is ACTIVE HIGH. |

| DATA[7:0] | 8               | Bi-directional | DATA[7:0] is an 8-bit wide data bus driven by the MAC in TRANSMIT state and by the PHY in all other states including SLEEP.  DATA[7:0] is synchronous to PCLK whether driven by the PHY or the MAC.  DATA[7:0] ONE is HIGH.                       |

# 8.1.3 CCA Interface

Table 3 – CCA Interface Signals

| SIGNAL     | Width<br>(Bits) | DIR              | DESCRIPTION                                                                                                          |

|------------|-----------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| CCA_STATUS | 1               |                  | The PHY returns CCA_STATUS after a CCA request is initiated by the MAC writing to the CCRE register via SERIAL_DATA. |

|            |                 | Slick            | CCA_STATUS is synchronous to PCLK.                                                                                   |

|            |                 | C <sub>1</sub> , | CCA_STATUS is ACTIVE HIGH.                                                                                           |

# 8.1.4 Management Interface

Table 4 – Management Interface Signals

| SIGNAL      | Width<br>(Bits) | DIR            | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERIAL_DATA | 1               | Bi-directional | The MAC writes control and address bits to SERIAL_DATA to initiate register access. SERIAL_DATA is driven by the MAC for Write operations. It is driven by the MAC for control and address parts of Read operations and by the PHY for the data part of Read operations.  SERIAL_DATA is synchronous to PCLK.  SERIAL_DATA ONE is HIGH. |

#### 8.2 PHY Operational State

Table 5 - PHY Readiness State

| STATE    | DESCRIPTION                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RESET    | Transitional state in which the configuration parameters are reset to default values. RESET is asynchronous to PCLK (see <u>11.1.1</u> ). |

| SLEEP    | The radio is off. PCLK is off (see 11.1.2).                                                                                               |

| STANDBY  | The radio is off. PCLK is on (unless STOPC is asserted). STANDBY is a higher activity state than SLEE.                                    |

| READY    | Parts of the radio are on. PCLK is on.                                                                                                    |

| TRANSMIT | The PHY Tx paths and the radio transmit path are active. PCLK is on.                                                                      |

| RECEIVE  | The PHY Rx paths and the radio receive path are active. PCLK is on.                                                                       |

# 9 Registers

In registers, bit positions that are defined as reserved shall be ignored on reading and set to ZERO on writing.

Two sets of parameters are defined to allow the MAC to control the operation of the PHY and permit information to be provided by the PHY to the MAC.

#### STATIC Parameters

These parameters are fixed for a given instantiation of the MAC and PHY. They can be considered to be constants for the purposes of the definition of the MAC-PHY Interface and their values can be defined in a given PHY data sheet, stored as constants in the system implementation or provided by any other means. The static parameters are defined in Table 6.

#### DYNAMIC Parameters

These parameters may be changed during operation of the system, and affect operation of the PHY. They shall be implemented within the PHY as registers and can be read and/or written (depending on the specific parameter) via the Serial Management Interface. The dynamic registers are defined in Table 7.

#### 9.1 Bit Ordering and Interpretation

All data structures, except where explicitly stated, are defined with the bit order as defined in Figure 4.

Reserved bits shall be ignored on reading and set to ZERO on writing.

#### 9.2 Register Address Spaces

The PHY interface shall have 256 addressable 8-bit registers (8-bit address, 8-bit data) divided into 3 regions:

Dynamic Register region defined by this specification: address 00(h)~1F(h)

Optional Static Parameter region defined by this specification: address 20(h)~7F(h)

Vendor Specific Register region for vender defined registers: address 80(h)~FF(h)

# 9.3 Static Parameter Definitions

**Table 6 – Description of Static Parameters**

| REGISTER             | OCTETS | DEFINITION                                                                |

|----------------------|--------|---------------------------------------------------------------------------|

| SupportedRegDomains  | 2      | Supported regulatory regions. Bit set to ONE if supported, ZERO otherwise |

|                      |        | First Octet                                                               |

|                      |        | Bit Domain                                                                |

|                      |        | [2:0] Reserved                                                            |

|                      |        | [3] European Telecommunications Standards Institute (ETSI)                |

|                      |        | [4] Federal Communications Commission (FCC)                               |

|                      |        | [5] Industry Canada (IC)                                                  |

|                      |        | [6] Association of Radio Industries and Businesses (ARIB)                 |

|                      |        | [7] Ministry of Information and Communications (MIC)                      |

|                      |        | Second Octet                                                              |

|                      |        | Bit Domain                                                                |

|                      |        | [7:0] Reserved                                                            |

| SupportedDataRates   | 2      | Set of supported data rates, Bit set to ONE if supported, ZERO otherwise  |

|                      |        | Bit Data Rate Supported                                                   |

|                      |        | [0] 53,33 Mbps                                                            |

|                      |        | [1] RESERVED                                                              |

|                      |        | [2] 80 Mbps                                                               |

|                      |        | [3] 106,7 Mbps                                                            |

|                      |        | [4] RESERVED                                                              |

|                      |        | [5] 160 Mbps                                                              |

|                      | U U    | [6] 200 Mbps                                                              |

|                      | at )   | [7] 320 Mbps                                                              |

|                      | Click  | [8] 400 Mbps                                                              |

|                      |        | [9] 480 Mbps                                                              |

|                      |        | [15:10] RESERVED                                                          |

| NumChannelsSupported | 1      | Number of supported channels                                              |

Table 6 – Description of Static Parameters (continued)

| REGISTER           | OCTETS | DEFINITION                                                                                                                                                                  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SupportedDiversity | 1      | Number of additional antennas provided for diversity                                                                                                                        |

|                    |        | [1:0] Number of additional receive antennas                                                                                                                                 |

|                    |        | [3:2] Reserved                                                                                                                                                              |

|                    |        | [5:4] Number of additional transmit antennas                                                                                                                                |

|                    |        | [7:6] Reserved                                                                                                                                                              |

| SupportedChannels  | 1      | Supported Channels. Bit set to ONE if supported, ZERO otherwise                                                                                                             |

|                    |        | Bit Channel Supported                                                                                                                                                       |

|                    |        | [0] TFC channels in band group 1 supported                                                                                                                                  |

|                    |        | [0] TFC channels in band group 1 supported [1] TFC channels in band group 2 supported [2] TFC channels in band group 3 supported [3] TFC channels in band group 4 supported |

|                    |        | [2] TFC channels in band group 3 supported                                                                                                                                  |

|                    |        | [3] TFC channels in band group 4 supported                                                                                                                                  |

|                    |        | [4] TFC channels in band group 5 supported                                                                                                                                  |

|                    |        | [5] TFC channels in band group 6 supported                                                                                                                                  |

|                    |        | [7:6] RESERVED                                                                                                                                                              |

| TXPowerLevel       | 16     | Array of transmit power levels.                                                                                                                                             |

|                    |        | Each element from 0 to (NumTxPowerLevels-1) of the array holds a                                                                                                            |

|                    |        | supported transmit power. The format of the power level datum is PHY vendor specific. The other elements shall be set to zero.                                              |

|                    |        | Element 0 shall hold the maximum transmit power supported.                                                                                                                  |

| NumTxPowerLevels   | 1      | Number of transmit power levels supported. Permitted range (015) with 0                                                                                                     |

| Numital owerLevels | '      | meaning a single fixed power level only.                                                                                                                                    |

|                    |        | [3:0] number of levels (permitted range 015)                                                                                                                                |

|                    |        | [7:4] RESERVED                                                                                                                                                              |

| SupportedPHYStates | 1      | Supported PHY States. Bit set to ONE if supported, ZERO otherwise.                                                                                                          |

|                    |        | [0] SLEEP                                                                                                                                                                   |

|                    |        | [1] STANDBY                                                                                                                                                                 |

|                    |        | [2] READY                                                                                                                                                                   |

|                    | ON     | [3] TRANSMIT                                                                                                                                                                |

|                    |        | [4] RECEIVE                                                                                                                                                                 |

|                    | 1.     | [7:5] RESERVED                                                                                                                                                              |

| PHYClockAccuracy   | 1      | Accuracy of PHY clock in parts per million.                                                                                                                                 |

| PHYResetTime       | 1      | Interval during which !PHY_RESET shall be held asserted for the PHY to                                                                                                      |

|                    |        | perform the RESET operation. Units us.                                                                                                                                      |

Table 6 – Description of Static Parameters (continued)

| REGISTER        | OCTETS  | DEFINITION                                                                                                                                                                                                                                              |

|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WakeUpDelay     | 2       | Time to transition from SLEEP mode to STANDBY mode. Units 0,5 μs.                                                                                                                                                                                       |

| TurnOnDelay     | 2       | Radio turn-on time during transition from STANDBY mode to READY mode. Units 0,5 µs.                                                                                                                                                                     |

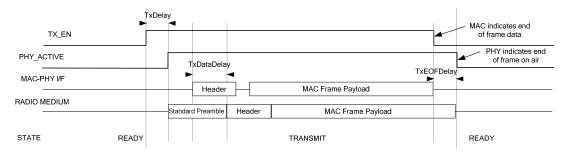

| TxDataDelay     | 1       | Delay, not greater than 4 $\mu$ s, before the end of the preamble at the local antenna before which the PHY will not assert DATA_EN to request the first octet of header data. (See $\underline{11.4}$ )Units $\mu$ s.                                  |

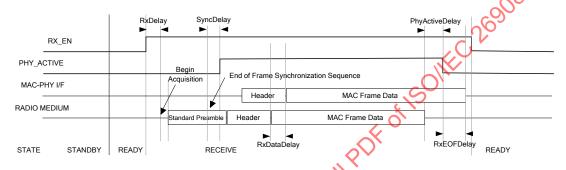

| RxDataDelay     | 2       | Maximum delay from the end of the received PLCP header at the local antenna to the transfer of the last octet of the PLCP header and HeaderError octet across the MAC-PHY interface. Units ns                                                           |

| TxEOFDelay      | 2       | Minimum delay from the transfer of the last octet of the frame across the MAC-PHY interface to the end of the frame at the local antenna. Units ns                                                                                                      |

| RxEOFDelay53.3  | 2       | Maximum delay, at 53,3 Mbps, from the de-assertion of PHY_ACTIVE to the last de-assertion of DATA_EN corresponding to the transfer of the last octet of the frame and receive quality block across the MAC-PHY. Units: PCLK cycles                      |

| RxEOFDelayOther | 2       | Maximum delay, at all rates other than 53,3 Mbps, from the de-assertion of PHY_ACTIVE to the de-assertion of the last DATA_EN corresponding to the transfer of last octet of the frame and receive quality block across the MAC-PHY. Units: PCLK cycles |

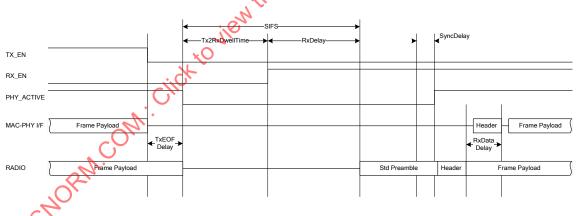

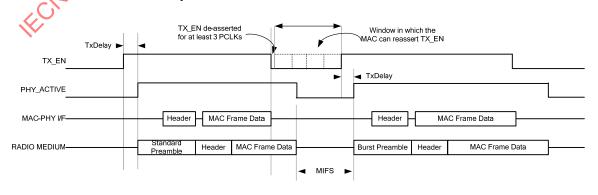

| TxDelay         | 2       | Delay from the rising edge of TX_EN to the time when the PHY feeds the leading edge of the preamble waveform to the antenna. Units ns.                                                                                                                  |

| RxDelay         | 2       | Delay from the rising edge of RX_EN to the time when the PHY begins the preamble accurisition processing. Units ns.                                                                                                                                     |

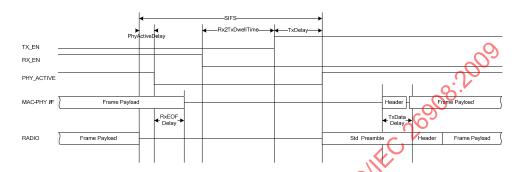

| Tx2RxDwellTime  | 2       | Minimum interval between PHY_ACTIVE de-assertion (in TRANSMIT State) and RX_EN assertion. Units ns.                                                                                                                                                     |

| Rx2TxDwellTime  | 2       | Minimum interval between RX_EN de-assertion and TX_EN assertion. Units ns.                                                                                                                                                                              |

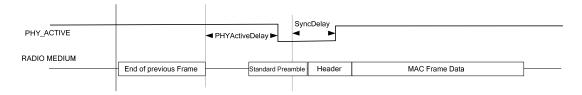

| SyncDelay       | 2 Click | Delay from the end of the last symbol of the Frame Synchronization Sequence of the preamble waveform in the local antenna to the time when the PHY asserts PHY_ACTIVE.                                                                                  |

| JORM.CC         |         | Note that since the preamble arrives asynchronously with respect to PCLK, PHY vendors should provide this value for the shortest amount of time before PHY_ACTIVE could be asserted assuming optimal alignment of the received preamble and PCLK.       |

|                 |         | Units ns.                                                                                                                                                                                                                                               |

| TxSetupTime     | 2       | Minimum time between setting of transmit control registers and assertion of TX_EN. Range defined in Table 8.                                                                                                                                            |

|                 |         | Units PCLK cycles.                                                                                                                                                                                                                                      |

Table 6 – Description of Static Parameters (continued)

| REGISTER          | OCTETS | DEFINITION                                                                                                                                                                                                                                          |

|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxSetupTime       | 2      | Minimum time between setting of receive control registers and the assertion of RX_EN or de-assertion of PHY_ACTIVE. Range defined in Table 8.                                                                                                       |

|                   |        | Units PCLK cycles.                                                                                                                                                                                                                                  |

| TxHoldTime        | 2      | Minimum time between the assertion of TX_EN and changing transmit control registers for the next frame. Range defined in Table 8.                                                                                                                   |

|                   |        | Units PCLK cycles.                                                                                                                                                                                                                                  |

| RxHoldTime        | 2      | Minimum time between the assertion of RX_EN or deassertion of PHY_ACTIVE and changing receive control registers for the next frame. Range defined in Table 8.                                                                                       |

|                   |        | Units PCLK cycles.                                                                                                                                                                                                                                  |

| PHYID             | 2      | PHY identifier to specify vendor, product and version. See Annex B for format and coding.                                                                                                                                                           |

| PHYVersion        | 1      | Edition of the ISO/IEC 26907 PHY specification supported. See Annex B for format and coding.                                                                                                                                                        |

| PHYActiveDelay    | 2      | Delay from the end of the last symbol of the frame received in the local antenna and PHY_ACTIVE de-assertion.                                                                                                                                       |

|                   |        | Note that since received frames arrive asynchronously with respect to PCLK, PHY vendors should provide this value for the shortest amount of time before PHY_ACTIVE could be de-asserted assuming optimal alignment of the received frame and PCLK. |

| 221/11/2          |        | Units ns.                                                                                                                                                                                                                                           |

| CCAValidTime      | 1      | Interval following the MAC setting CCRE = ONE after which the PHY should respond with the CCA measurement result.                                                                                                                                   |

|                   |        | Units 0,5 µs.                                                                                                                                                                                                                                       |

| MinPTChangeLength | 1      | Minimum MACFrame Payload length for the preamble type of the next frame to be different to the current frame.                                                                                                                                       |

|                   |        | Fixed value = 1 octet                                                                                                                                                                                                                               |

| RangingSupported  | 1      | Support of ranging                                                                                                                                                                                                                                  |

|                   | 2      | [0] Set to ONE if supported, otherwise set to ZERO                                                                                                                                                                                                  |

|                   | CON    | [1] Support for 528MHz precision (Mandatory)                                                                                                                                                                                                        |

|                   | ~ V.   | [2] Support for 1 056MHz precision                                                                                                                                                                                                                  |

|                   | 5/4.   | [3] Support for 2 112MHz precision                                                                                                                                                                                                                  |

|                   |        | [4] Support for 4 224MHz precision                                                                                                                                                                                                                  |

|                   |        | [5] Support for RANGINGTIMER [23:16]                                                                                                                                                                                                                |

| ECHO              |        | [6] Support for RANGINGTIMER [31:24]                                                                                                                                                                                                                |

|                   |        | [7] RESERVED                                                                                                                                                                                                                                        |

Table 6 - Description of Static Parameters (concluded)

| REGISTER             | OCTETS | DEFINITION                                                              |

|----------------------|--------|-------------------------------------------------------------------------|

| RANGING_TRANSMIT_    | 2      | See 14.5 in ISO/IEC 26907 for the definition of RANGING_TRANSMIT_DELAY. |

| DELAY                |        | Units 1 / 4 224 MHz - same as RANGINGTIMER (see Table 7)                |

| RANGING_RECEIVE_     | 2      | See 14.5 in ISO/IEC 26907 for the definition of RANGING_RECEIVE_DELAY.  |

| DELAY                |        | Units 1 / 4 224 MHz - same as RANGINGTIMER (see Table 7)                |

| STOP_OFF             | 1      | Number of PCLK cycles from de-assertion of STOPC to PCLK stable.        |

|                      |        | Units PCLK cycles                                                       |

| ToneNullingSupported | 1      | Level of support for Tone-Nulling information                           |

|                      |        | [0] Set to ONE if supported, otherwise set to ZERO                      |

|                      |        | [7:1] RESERVED                                                          |

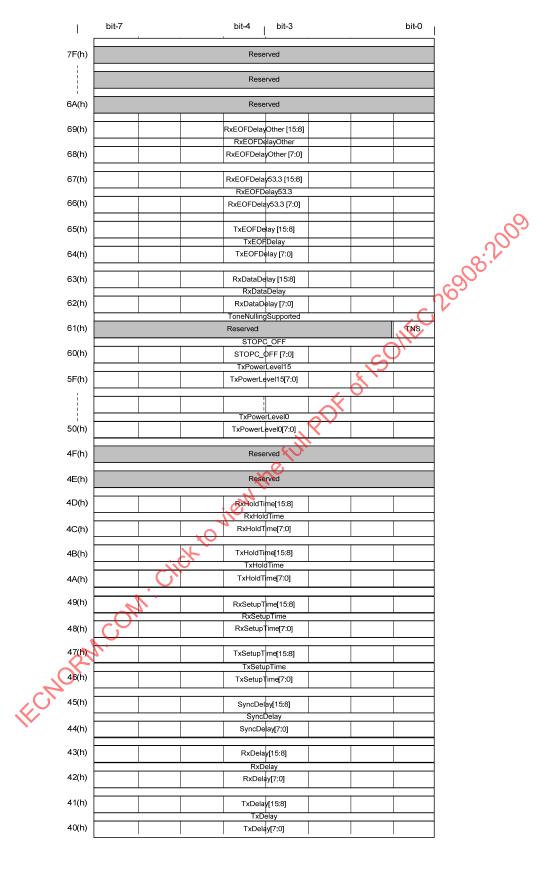

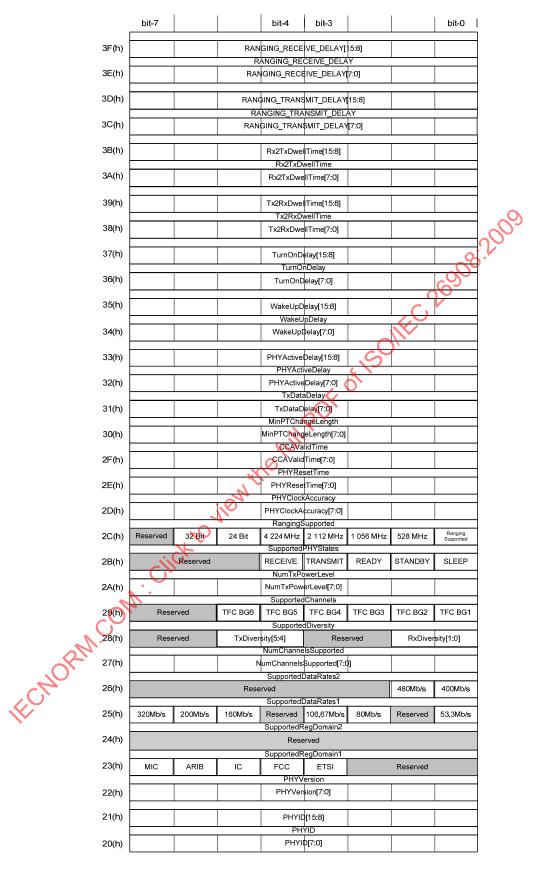

# 9.4 Static Parameter Coding

should be 3. Shipping the full part of the other of the other of the other of the other ot If the values of the static parameters are stored in the PHY, they should be implemented as read only values using the addresses and formats defined in Figure 2 and Figure 3 using the addresses and formats defined in Figure 2 and Figure 3.

Figure 2 - Static Parameter Encoding 40(h) -7F(h)

Figure 3 – Static Parameter Encoding 20(h) - 3F(h)

# 9.5 Dynamic Register Definitions

All registers in the Dynamic Register area are readable (R) and writable (W) by the MAC except RDY in the CONTROL register and RANGINGTIMER which are Read Only.

NOTE Although the Current Regulatory Domain (CRD) register is both readable and writable, the end-user should not be given the ability to change the contents at will. Some regulatory regions may have strict requirements in this regard.

Table 7 - Description of Dynamic Registers

| Addr. | Register | R/W      | Descripti | ion                                                                                                                                                                                                                      | Init. |

|-------|----------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 00(h) | CONTROL  | R/W      | PHY Cor   | ntrol register                                                                                                                                                                                                           | Q(h)  |

|       |          | (Except  | [0]       | ntrol register  RDY - Result of !PHY_RESET  ZERO = Normal completion of initialization  ONE = Abnormal completion of initialization  Reserved  RNGEN  ZERO = Ranging disabled  ONE = Ranging enabled  CCRE - CCA Request |       |

|       |          | RDY      |           | ZERO = Normal completion of initialization                                                                                                                                                                               |       |

|       |          | which is |           | ONE = Abnormal completion of initialization                                                                                                                                                                              |       |

|       |          | R)       | [1]       | Reserved                                                                                                                                                                                                                 |       |

|       |          |          | [2]       | RNGEN                                                                                                                                                                                                                    |       |

|       |          |          |           | ZERO = Ranging disabled                                                                                                                                                                                                  |       |

|       |          |          |           | ONE = Ranging enabled                                                                                                                                                                                                    |       |

|       |          |          | [3]       | CCRE – CCA Request                                                                                                                                                                                                       |       |

|       |          |          |           | ZERO = Stop CCA estimation                                                                                                                                                                                               |       |

|       |          |          |           | ONE = Start CCA estimation                                                                                                                                                                                               |       |

|       |          |          | [7:4]     | RESERVED                                                                                                                                                                                                                 |       |

| 01(h) | CRD      | R/W      | [2:0]     | RESERVED                                                                                                                                                                                                                 | 0(h)  |

|       |          |          | [7:3]     | CRD – Current regulatory domain                                                                                                                                                                                          |       |

|       |          |          | Each do   | main is mapped to a bit in the register, as follows:                                                                                                                                                                     |       |

|       |          |          | Bit       | Domain                                                                                                                                                                                                                   |       |

|       |          |          | 3         | European Telecommunications Standards  institute (ETSI).                                                                                                                                                                 |       |

|       |          |          | 4         | Federal Communications Commission (FCC).                                                                                                                                                                                 |       |

|       |          |          | 5 .       | Industry Canada (IC).                                                                                                                                                                                                    |       |

|       |          | C        | 6         | Association of Radio Industries and Businesses (ARIB).                                                                                                                                                                   |       |

|       |          | W.       | 7         | Ministry of Information and Communication (MIC)                                                                                                                                                                          |       |

| 02(h) | TXCHAN   | R/W      |           | TXCH - Channel of next transmitted frame                                                                                                                                                                                 | 0(h)  |

|       | CH2      |          | [2:0]     | TFC[2:0] – least-significant 3 bits of TFC                                                                                                                                                                               |       |

|       | (K)      |          | [5:3]     | BG[2:0] – 3-bit Band Group                                                                                                                                                                                               |       |

|       |          |          | [6]       | TFC[3] – most-significant bit of TFC                                                                                                                                                                                     |       |

|       |          |          | [7]       | RESERVED                                                                                                                                                                                                                 |       |

|       |          |          | (NOTE:    | TXCH is coded as a 3-bit Band Group and a 4-bit TFC.E                                                                                                                                                                    |       |

|       |          |          |           | 2 of ISO/IEC 26907 for the mapping of Channel Number to oup and TFC)                                                                                                                                                     |       |

Table 7 – Description of Dynamic Registers (continued)

| Addr. | Register | R/W  | Description                                                                         | Init. |

|-------|----------|------|-------------------------------------------------------------------------------------|-------|

| 03(h) | TXCTL    | R/W  | Transmit Control                                                                    | 0(h)  |

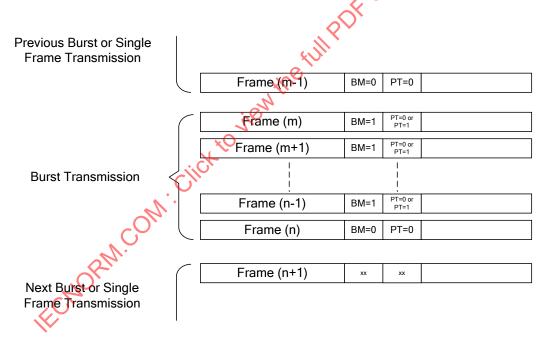

|       |          |      | [0] TXPT – Preamble type of next transmitted frame.                                 |       |

|       |          |      | ZERO = Standard Preamble                                                            |       |

|       |          |      | ONE = Burst Preamble                                                                |       |

|       |          |      | [1] Reserved                                                                        |       |

|       |          |      | [3:2] TXANT – Transmit antenna to be used.  Value 0SupportedDiversity[5:4] where:   |       |

|       |          |      | 00 identifies transmit antenna 1                                                    |       |

|       |          |      | 01 identifies transmit antenna 2                                                    |       |

|       |          |      | 10 identifies transmit antenna 3                                                    |       |

|       |          |      | 11 identifies transmit antenna 4                                                    |       |

|       |          |      | [7:4] TXPWR – Index into TxPowerLevels for transmit power level                     |       |

| 04(h) | RXCHAN   | R/W  | RXCH – Channel of next received frame                                               | 0(h)  |

|       |          |      | [2:0] TFC[2:0] – least-significant 3 bits of TFC                                    |       |

|       |          |      | [5:3] BG[2:0] – 3-bit Band Group                                                    |       |

|       |          |      | [6] TFC[3] – most-significant bit of TFC                                            |       |

|       |          |      | [7] RESERVED                                                                        |       |

|       |          |      | (See 11.2 of ISO/IEC 26907 for the mapping of Channel Number to Band Group and TFC) |       |

| 05(h) | RXCTL    | R/W  | Receive Control                                                                     | 0(h)  |

|       |          |      | [0] RXPT - Preamble type of next received frame                                     |       |

|       |          |      | ZERO = Standard Preamble                                                            |       |

|       |          |      | ONE = Burst Preamble                                                                |       |

|       |          | ciji | [1] PTON (R/W)                                                                      |       |

|       |          | W.,  | ZERO = PHY does not process PT bit in PLCP header                                   |       |

|       |          |      | ONE = PHY does process PT bit in PLCP header                                        |       |

|       | CHORMICE |      | [3:2] RXANT – Receive antenna to be used.  Value 0SupportedDiversity[1:0] where:    |       |

|       |          |      | 00 identifies receive antenna 1                                                     |       |

|       |          |      | 01 identifies receive antenna 2                                                     |       |

|       |          |      | 10 identifies receive antenna 3                                                     |       |

|       |          |      | 11 identifies receive antenna 4                                                     |       |

|       |          |      | [7:4] RESERVED                                                                      |       |

Table 7 – Description of Dynamic Registers (concluded)

| Addr.            | Register        | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Init. |

|------------------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 06(h)            | PMMODE          | R/W | [2:0] Power management mode. Values:  0 READY  1 STANDBY  2 SLEEP  3-7 RESERVED  [7:3] RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1(h)  |

| 07(h) –<br>0A(h) | RANGINGTIMER    | R   | Ranging Timer (units 1 / 4 224MHz)  [31:0] RANGINGTIMER – 32-bit ranging counter value  Note that this register requires multiple read operations (07(h) to 0A(h)) to retrieve the full value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0(h)  |

| 0B(h)            | CRDExtension    | R/W | Extension for 2 <sup>nd</sup> Octet of Regulatory domains [7:0] RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0(h)  |

| 0C(h)            | WTONEMAPADDRESS | R/W | Tone-Nulling Map Address  [3:0] ADDRESS - address used by WTONENULLDATA to select which set of 8 Tone Nulls to be written or read  [5:4] BAND - Selected band within the Band Group  00 = Lower band of frequencies in the Band Group  01 = Middle band of frequencies in the Band Group  10 = Upper band of frequencies in the Band Group  11 = Only used when bit 6 is set to ONE to reset the tone-nulling map for all band IDs  [6] RESET - When set to ONE will reset all tone-nulling map values for the band of frequencies selected by WTONEMAPADDRESS[5:4]  [7] Reserved  NOTE  Bits [5:0] will auto post increment, wrapping from 0b101111 to 0b0000000 on every access to WTONENULLDATA  NOTE  See 9.2 Tone-Nulling in ISO/IEC 26907. | 0(h)  |

| 0D(h)            | WTONENULLDATA   | R/W | Tone-Nulling Data  [7:0] The value of the 8 tone nulls addressed by WTONEMAPADDRESS. For each bit in WTONENULLDATA  ZERO = Tone is to be nulled  ONE =Tone is not to be nulled (reset value)  NOTE  Every access to this register will cause bit [5:0] of WTONEMAPADDRESS to post increment with wrap.                                                                                                                                                                                                                                                                                                                                                                                                                                           | ff(h) |

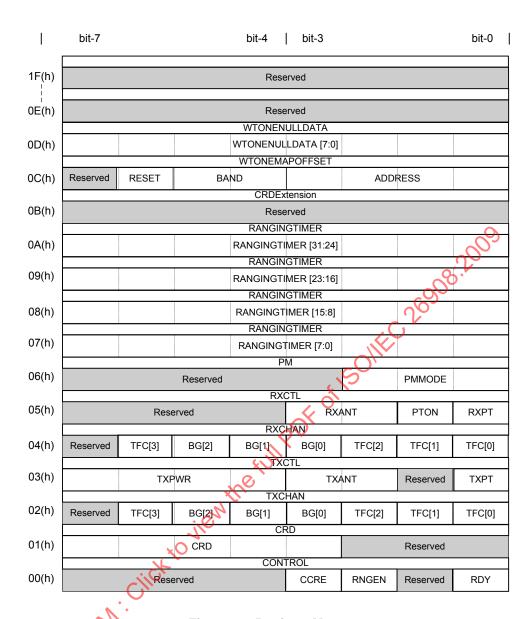

# 9.6 Register Map

Figure 4 shows the register map. Gray portions in the map are reserved.

Figure 4 - Register Map

# 9.7 Register Set Access Timing

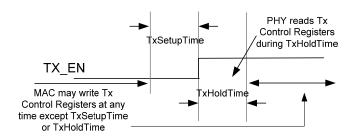

# 9.7.1 Transmit Control Registers

Figure 5 - Transmit Control Register Setup & Hold

TXCHAN and TXCTL (TXPT, TXANT and TXPWR) are registers used to specify parameters for the next transmit frame operation. As defined in Figure 5, they shall be set by the MAC at least TxSetupTime PCLK

cycles before the assertion of TX\_EN and are held stable for at least TxHoldTime PCLK cycles. The PHY shall read these registers within this TxHoldTime period. The values of these registers then control the parameters for the transmit frame operation corresponding to this TX\_EN assertion.

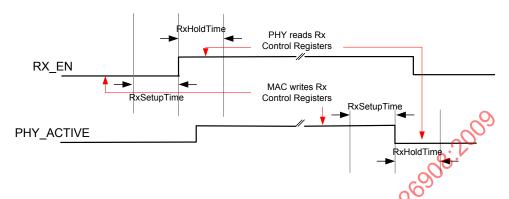

#### 9.7.2 Receive Control Registers

Figure 6 - Receive Control Register Setup & Hold

RXCHAN and RXCTL (RXPT and RXANT) are registers used to specify parameters for the next receive frame operation. As defined in Figure 6, they shall be set by the MAC at least RxSetupTime PCLK cycles before the assertion of RX\_EN and are held stable for at least RxHoldTime PCLK cycles. The PHY shall read these registers in this RxHoldTime period ignoring any PTON setting and any previous BM or PT settings. The values of these registers then control the parameters for the receive frame operation corresponding to this RX\_EN assertion.

For burst mode reception, the MAC shall set the registers for the next receive frame operation at least RxSetupTime PCLK cycles before PHY\_ACTIVE de-assertion indicating the end of frame reception. The PHY shall read the registers within RxHoldTime PCLK cycles following the de-assertion of PHY\_ACTIVE. These registers then control the parameters for the reception of the next frame if RX\_EN is not de-asserted. In receive burst mode (see <a href="https://linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear.org/linear

RX\_EN de-assertion and re-assertion has precedence over PHY\_ACTIVE de-assertion and will cause the PHY to overwrite any internal values loaded from the receive control registers.

Parameter Minimum Value Maximum Value (PCLK Periods) (PCLK Periods) **T**xSetupTime 0 128 0 TxHoldTime 128 RxSetupTime 0 128 RxHoldTime 0 128

Table 8 - Register Access Parameter Values

#### 9.8 TONE-NULLING MAP CONTROL

At any time respecting the setup and hold timings, the MAC may write the tone-nulling information to the PHY. WTONEMAPADDRESS and WTONENULLDATA are not Transmit Control or Receive Control registers and do not require double buffering. The protocol for writing the tone-nulling information is an address followed by data protocol with auto address post increment.

Writing WTONEMAPADDRESS sets the address pointer in the PHY to the data location of the first tone to be accessed. Subsequent read/writes to WTONENULLDATA will retrieve/update the tone-nulling information of 8

tones per access while post incrementing the address pointer in the PHY. Setting bits to ZERO indicates that the tone is to be nulled.

Table 9 - Tone-Nulling Mapping to PHY Parameters

| WTONEMAPADDRESS   |                      | Frequency             |                          |  |

|-------------------|----------------------|-----------------------|--------------------------|--|

| bit [5:4]<br>BAND | bit [3:0]<br>ADDRESS | Band in Band<br>Group | Subcarriers<br>(LSB MSB) |  |

| 0b00              | 0b0000               | Lower                 | -6457                    |  |